# 5 x 7 DOT MATRIX ALPHANUMERIC DISPLAY SYSTEM

HDSP - 2416 HDSP - 2424 HDSP - 2432

HDSP - 2440 HDSP - 2470

HDSP - 2471 HDSP - 2472

TENTATIVE DATA SEPTEMBER 1978

#### **Features**

- COMPLETE ALPHANUMERIC DISPLAY SYSTEM UTILIZING THE HDSP-2000 DISPLAY

- CHOICE OF 64, 128, OR USER DEFINED ASCII CHARACTER SET

- CHOICE OF 16, 24, 32, or 40 ELEMENT DISPLAY PANEL

- MULTIPLE DATA ENTRY FORMATS Left, Right, RAM, or Block Entry

- EDITING FEATURES THAT INCLUDE CURSOR, BACKSPACE, FORWARDSPACE, INSERT, DELETE, AND CLEAR

- DATA OUTPUT CAPABILITY

- SINGLE 5.0 VOLT POWER SUPPLY

- TTL COMPATIBLE

- EASILY INTERFACED TO A KEYBOARD OR A MICROPROCESSOR

# Description

The HDSP-24XX series of alphanumeric display systems provides the user with a completely supported 5 x 7 dot matrix display panel. These products free the user's system from display maintenance and minimize the interaction normally required for alphanumeric displays. Each alphanumeric display system is composed of two component parts:

- An alphanumeric display controller which consists of a preprogrammed microprocessor plus associated logic, which provides decode, memory, and drive signals necessary to properly interface a user's system to an HDSP-2000 display. In addition to these basic display support operations, the controller accepts data in any of four data entry formats and incorporates several powerful editing routines.

- 2. A display panel which consists of HDSP-2000 displays matched for luminous intensity and mounted on a P.C. board designed to have low thermal resistance.

These alphanumeric display systems are attractive for applications such as data entry terminals, instrumentation, electronic typewriters, and other products which require an easy to use 5 x 7 dot matrix alphanumeric display system.

### PART NUMBER DESCRIPTION

# Display Boards HDSP-2416 Single-line 16 character display panel utilizing the HDSP-2000 display HDSP-2424 Single-line 24 character display panel utilizing the HDSP-2000 display HDSP-2432 Single-line 32 character display panel utilizing the HDSP-2000 display HDSP-2440 Single-line 40 character display panel utilizing the HDSP-2000 display Controller Boards

HDSP-2470 HDSP-2000 display interface incorporating a 64 character ASCII decoder

HDSP-2471 HDSP-2000 display interface incorporating a 128 character ASCII decoder

HDSP-2472 HDSP-2000 display interface without ASCII decoder. Instead, a 24 pin socket is provided to accept a custom 128 character set from a user programmed 1K x 8 PROM.

When ordering, specify one each of the Controller Board and the Display Board for each complete system.

# HDSP-2470/-2471/-2472

# **Absolute Maximum Ratings**

| Vcc0.5V to 6.0V                                                           |

|---------------------------------------------------------------------------|

| Operating Temperature Range, Ambient (T <sub>A</sub> ) 0°C to 70°C        |

| Storage Temperature Range (Ts)55°C to 100°C                               |

| Voltage Applied to any Input or Output0.5V to 6.0V                        |

| ISOURCE Continuous for any Column Driver 5.0 Amps (60 sec. max. duration) |

# Recommended Operating Conditions

| Parameter                  | Symbol  | Min. | Max. | Units |

|----------------------------|---------|------|------|-------|

| Supply Voltage             | Vcc     | 4.75 | 5.25 | ٧     |

| Data Out                   | loL     |      | 0.4  | mA    |

| Data Out                   | Гон     |      | -20  | μΑ    |

| Ready, Data Valid,         | loL     |      | 1.6  | mA    |

| Column On, Display<br>Data | Іон     |      | -40  | μА    |

| Cleak                      | loL     |      | 10.0 | mA    |

| Clock                      | Гон     |      | -1.0 | mA    |

| Column <sub>1-5</sub>      | ISOURCE |      | -5.0 | Α     |

# Electrical Characteristics Over Operating Temperature Range

(Unless otherwise specified)

| Parameter                                   | Symbol  | Min. | Тур. | Max. | Units | Conditio                                      | ns                      |

|---------------------------------------------|---------|------|------|------|-------|-----------------------------------------------|-------------------------|

| Supply Current <sup>[1]</sup>               | Icc     |      |      | 400  | mA    | V <sub>CC</sub> = 5.25V Colum<br>Outputs Open | nn On and All           |

| Input Threshold High (except Reset)         | ViH     | 2.0  |      |      | ٧     | $V_{CC} = 5.0V \pm .25V$                      |                         |

| Input Threshold High — Reset <sup>[2]</sup> | ViH     | 3.0  |      |      | ٧     | $V_{CC} = 5.0V \pm .25V$                      |                         |

| Input Threshold Low — All Inputs            | VIL     |      |      | 0.8  | ٧     | $V_{CC} = 5.0V \pm .25V$                      |                         |

| Data Out Valtage                            | VonData | 2.4  |      |      | ٧     | $I_{OH} = -20\mu A$                           | $V_{CC} = 4.75V$        |

| Data Out Voltage                            | VolData |      |      | 0.5  | ٧     | I <sub>OL</sub> = 0.4mA                       | $V_{CC} = 4.75V$        |

|                                             | VohClk  | 2.4  |      |      | ٧     | $I_{OH} = -1000 \mu A$                        | $V_{CC} = 4.75V$        |

| Clock Output Voltage                        | VolClk  |      |      | 0.5  | ٧     | I <sub>OL</sub> = 10.0mA                      | Vcc = 4.75V             |

| Ready, Display Data, Data Valid,            | Voн     | 2.4  |      |      | ٧     | $IOH = -40\mu A$                              | $V_{CC} = 4.75V$        |

| Column on Output Voltage                    | VoL     |      |      | 0.5  | ٧     | IOL = 1.6mA                                   | $V_{CC} = 4.75V$        |

| Input Current,[3] All Inputs Except         | lin -   |      |      | -0.3 | mA    | V <sub>IH</sub> = 2.4V                        | $V_{CC} = 5.25V$        |

| Reset, Chip Select, D7                      | liL     |      |      | -0.6 | mA    | V <sub>IL</sub> = 0.5V                        | V <sub>CC</sub> = 5.25V |

| Reset Input Current                         | liH     |      |      | -0.3 | mA    | V <sub>IH</sub> = 3.0V                        | Vcc = 5.25V             |

|                                             | liL     |      |      | -0.6 | mA    | V <sub>IL</sub> = 0.5V                        | Vcc = 5.25V             |

| Chip Select, D7 Input Current               | lı lı   | -10  |      | +10  | μА    | 0 < V1 < Vcc                                  |                         |

| Column Output Voltage                       | VOLCOL  | 2.6  | 3.2  |      | V     | IOUT = -5.0A                                  | VCC = 5.00V             |

#### NOTES:

- 1. See Figure 11 for total system supply current.

- External reset may be initiated by grounding Reset with either a switch or TTL gate for a minimum time of 50ms. For Power On Reset to function properly, Vcc power supply should turn on at a rate > 100V/s.

- Momentary peak surge currents may exist on these lines. However, these momentary currents will not interfere with proper operation of the HDSP-2470/1/2.

## HDSP-2416/-2424/-2432/-2440

# **Absolute Maximum Ratings**

| Supply Voltage Vcc to Ground     | -0.5V to 6.0V |

|----------------------------------|---------------|

| Inputs, Data Out and VB          | -0.5V to Vcc  |

| Column Input Voltage, VCOL       | 0.5V to +6.0V |

| Free Air Operating Temperature   |               |

| Range, TA <sup>[1]</sup>         | 0°C to +55°C  |

| Storage Temperature Range, Ts55° | °C to +100°C  |

# Recommended Operating Conditions

| Parameter                                              | Symbol    | Min. | Norm. | Max. | Units |

|--------------------------------------------------------|-----------|------|-------|------|-------|

| Supply Voltage                                         | Vcc       | 4.75 | 5.0   | 5.25 | V     |

| Column Input<br>Voltage, Column On                     | Vcol      | 2.6  |       |      | ٧     |

| Setup Time                                             | tsetup    | 70   | 45    |      | ns    |

| Hold Time                                              | tHOLD     | 30   | 0     |      | ns    |

| Width of Clock                                         | tw(CLOCK) | 75   |       |      | ns    |

| Clock Frequency                                        | fcLock    | 0    |       | 3    | MHz   |

| Clock Transition<br>Time                               | tTHL      |      |       | 200  | ns    |

| Free Air Operating <sup>[1]</sup><br>Temperature Range | TA        | 0    |       | 55   | °C    |

# Electrical Characteristics Over Operating Temperature Range

(Unless otherwise specified)

| Parameter                                           |                        | Symbol  | Min. | Тур.* | Max.               | Units | Conditions                                                      |                       |  |

|-----------------------------------------------------|------------------------|---------|------|-------|--------------------|-------|-----------------------------------------------------------------|-----------------------|--|

| Supply Current                                      |                        |         |      | 45n   | 60n <sup>[2]</sup> | mA    |                                                                 | $V_B = 0.4V$          |  |

|                                                     |                        | loc     |      | 73n   | 95n                | mA    | VCLOCK=VDATA=2.4V<br>All SR Stages =<br>Logical 1               | V <sub>B</sub> = 2.4V |  |

| Column Current at any Column Input                  |                        | ICOL    |      |       | 1.5n               | mA    | V <sub>CC</sub> = V <sub>COL</sub> = 5.25V<br>All SR Stages =   | $V_B = 0.4V$          |  |

|                                                     |                        | ICOL    |      | 335n  | 410n               | mA    | Logical 1                                                       | V <sub>B</sub> = 2.4V |  |

| Peak Luminous Intensity per LED (Character Average) |                        | IV PEAK | 105  | 200   |                    | μcd   | $V_{CC} = 5.0V, V_{COL} = 5.0V, V_{COL} = 5.0V, V_{COL} = 5.0V$ |                       |  |

| VB, Clock or Data Input T                           | hreshold High          | VIH     | 2.0  |       |                    | V     | VCC = VCOL = 4.75V                                              |                       |  |

| VB, Clock or Data Input                             | Threshold Low          | VIL     |      |       | 0.8                | V     |                                                                 |                       |  |

| Input Current Logical 1                             | V <sub>B</sub> , Clock | Іін     |      |       | 80                 | μΑ    | -V <sub>CC</sub> = 5.25V, V <sub>IH</sub> = 2.4V                |                       |  |

|                                                     | Data In                | Тін     |      |       | 40                 | μА    |                                                                 |                       |  |

| Input Current Logical 0                             | V <sub>B</sub> , Clock | IIL     |      | -500  | -800               | μА    |                                                                 |                       |  |

| Data In                                             |                        | lı∟     |      | -250  | -400               | μА    | $V_{CC} = 5.25V, V_{IL} = 0$                                    | .4V                   |  |

| Power Dissipation Per Board <sup>[4]</sup>          |                        | PD      |      | 0.66n |                    | W     | $V_{CC} = 5.0V$ , $V_{COL} = 15$ LED's on per Char $V_B = 2.4V$ |                       |  |

<sup>\*</sup>All typical values specified at V<sub>CC</sub> = 5.0V and T<sub>A</sub> = 25°C unless otherwise noted.

#### NOTES:

- 1. Operation above 55°C (70°C MAX) may be achieved by the use of forced air (150 fpm normal to component side of HDSP-247X controller board at sea level).

- 2. n = number of HDSP-2000 packages

HDSP-2416 n = 4

HDSP-2424 n = 6

HDSP-2432 n = 8

HDSP-2440 n = 10

- 3. Tj refers to initial case temperature immediately prior to the light measurement.

- 4. Power dissipation with all characters illuminated.

#### **System Overview**

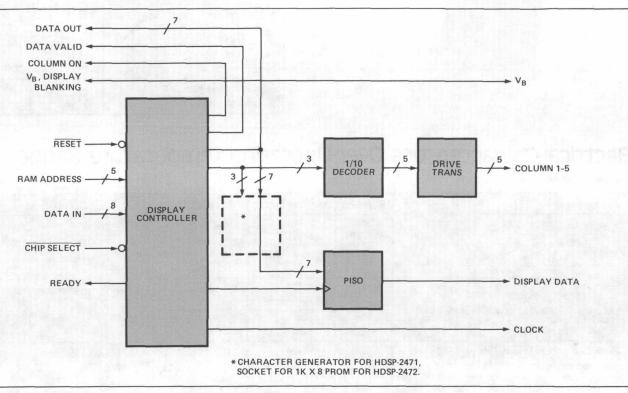

The HDSP-2470/-2471/-2472 Alphanumeric Display Controllers provide the interface between any ASCII based Alphanumeric System and the HDSP-2000 Alphanumeric Display. ASCII data is loaded into the system by means of any one of four data entry modes — Left, Right, RAM or Block Entry. This ASCII data is stored in the internal RAM memory of the system. The system refreshes HDSP-2000 displays from 4 to 48 characters with the decoded data.

The user interfaces to any of the systems through eight DATA IN inputs, five ADDRESS inputs (RAM mode), a CHIP SELECT input, RESET input, seven DATA OUT

outputs, a READY output, DATA VALID output, and a COLUMN ON output. A low level on the RESET input clears the display and initializes the system. A low level on the CHIP SELECT input causes the system to load data from the DATA IN and ADDRESS inputs into the system. The controller outputs a status word, cursor address and 32 ASCII data characters through the DATA OUT outputs and DATA VALID output during the time the system is waiting to refresh the next column of the display. The COLUMN ON output can be used to synchronize the DATA OUT function. A block diagram for the HDSP-2470/-2471/-2472 systems is shown in Figure 1.

Figure 1. Block Diagram for the HDSP-2470/-2471/-2472 Alphanumeric Display Controller.

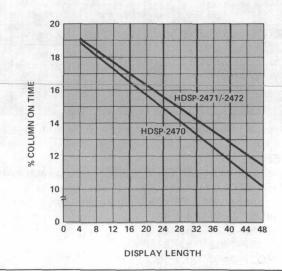

The system interfaces to the HDSP-2000 display through five COLUMN outputs, a CLOCK output, DISPLAY DATA output, and the COLUMN ON output. The user should connect DISPLAY DATA to DATA IN of the leftmost HDSP-2000 cluster and cascade DATA OUT to DATA IN of all HDSP-2000 clusters. COLUMN outputs from the system are connected to the COLUMN inputs of all HDSP-2000 clusters. The HDSP-24XX Series display boards are designed to interconnect directly with the HDSP-247X Series display controllers. The COLUMN outputs can source enough current to drive up to 48 characters of the HDSP-2000 display. Pulse width modulation of display luminous intensity can be provided by connecting COLUMN ON to the input of a monostable multivibrator and the output of the monostable multivibrator to the VB inputs of the HDSP-2000 displays. The system is designed to refresh the display at a fixed refresh rate of 100 Hz. COLUMN ON time is optimized for each display length in order to maximize light output as shown in Figure 2.

Figure 2. Column on Time vs. Display Length for the HDSP-2470/-2471/-2472 Alphanumeric Display Controller.

#### Control Mode/Data Entry

User interface to the HDSP-247X Series controller is via an 8 bit word which provides to the controller either a control word or standard ASCII data input. In addition to this user provided 8 bit word, two additional control lines, CHIP SELECT and READY, allow easily generated "handshake" signals for interface purposes.

A logic low applied to the CHIP SELECT input (minimum six microseconds) causes the controller to read the 8 DATA IN lines and determine whether a control word or ASCII data word is present, as determined by the logic state of the most significant bit (D7). If the controller detects a logic high at D7, the state of D6-D0 will define the data entry mode and the number of alphanumeric characters to be displayed.

The 8 bit control data word format is outlined in Figure 3. For the control word ( $D_7$  high), bits  $D_6$  and  $D_5$  define the selected data entry mode (Left entry, Right entry, etc.) and bits  $D_3$  to  $D_0$  define display length. Bit  $D_4$  is ignored.

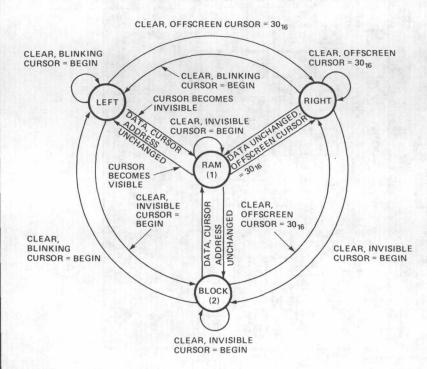

Control word inputs are first checked to verify that the control word is valid. The system ignores display lengths greater than 1011 for left block or right, or 0111 for RAM. If the word is valid, the present state—next state table shown in Figure 4 is utilized to determine whether or not to clear the display. For display lengths of up to 32 characters, RAM entry can be used as a powerful editing tool, or can be used to preload the cursor. With other transitions, the internal data memory is cleared.

CONTROL

WORD: D7D6D5D4D3D2D1D0

1 X X - Y Y Y Y

| YYYY    | DISPLAY LENGTH: |

|---------|-----------------|

| 0 0 0 0 | 4 DIGITS        |

| 0001    | 8 "             |

| 0010    | 12 "            |

| 0 0 1 1 | 16 "            |

| 0100    | 20 "            |

| 0 1 0 1 | 24 "            |

| 0110    | 28 "            |

| 0 1 1 1 | 32* "           |

| 1000    | 36 "            |

| 1001    | 40 "            |

| 1010    | 44 "            |

| 1011    | 48 "            |

\*maximum for RAM data entry mode

| XX  | DATA ENTRY MODES |

|-----|------------------|

| 0 0 | RAM DATA ENTRY   |

| 0 1 | LEFT DATA ENTRY  |

| 1 0 | RIGHT DATA ENTRY |

| 11  | BLOCK DATA ENTRY |

Figure 3. Control Word Format for the HDSP-2470/-2471/-2472 Alphanumeric Display Controller.

- (1) RAM ENTRY MODE IS VALID FOR DISPLAYS OF 32 CHARACTERS OR LESS IN LENGTH.

- (2) FOLLOWING A TRANSITION FROM RAM TO BLOCK, WHEN THE CURSOR ADDRESS IS 48 (30<sub>16</sub>) DURING THE TRANSITION, THE FIRST VALID ASCII CHARACTER WILL BE IGNORED AND THE SECOND VALID ASCII CHARACTER WILL BE LOADED IN THE LEFT- MOST DISPLAY LOCATION.

WHERE BEGIN IS DEFINED AS FOLLOWS:

| DISPLAY | CURSOR ADDRESS                      |

|---------|-------------------------------------|

| LENGTH  | OF BEGIN                            |

| 4       | 2C <sub>16</sub> , 44 <sub>10</sub> |

| 8       | 28 <sub>16</sub> , 40 <sub>10</sub> |

| 12      | 24 <sub>16</sub> , 36 <sub>10</sub> |

| 16      | 20 <sub>16</sub> , 32 <sub>10</sub> |

| 20      | 1C <sub>16</sub> , 28 <sub>10</sub> |

| 24      | 18 <sub>16</sub> , 24 <sub>10</sub> |

| 28      | 14 <sub>16</sub> , 20 <sub>10</sub> |

| 32      | 1016, 1610                          |

| 36      | 0C <sub>16</sub> , 12 <sub>10</sub> |

| 40      | 08 <sub>16</sub> , 8 <sub>10</sub>  |

| 44      | 0416, 410                           |

| 48      | 0016                                |

|         |                                     |

Figure 4. Present State-Next State Diagram for the HDSP-2470/-2472 Alphanumeric Display Controller.

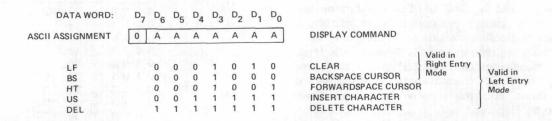

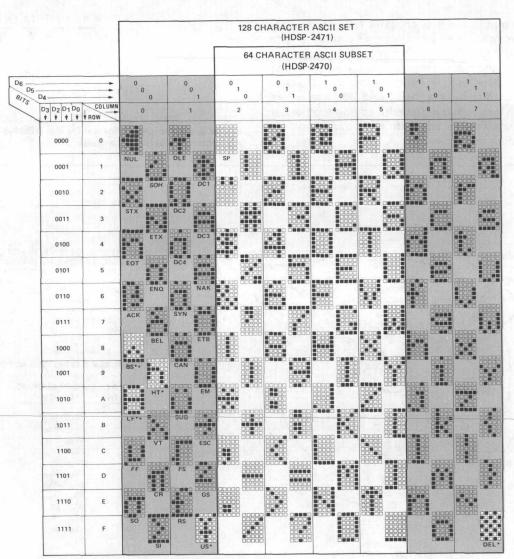

If D<sub>7</sub> is a logic low when the DATA IN lines are read, the controller will interpret D<sub>6</sub>-D<sub>0</sub> as standard ASCII data to be stored, decoded and displayed. The system accepts seven bit ASCII for all three versions. However, the HDSP-2470 system displays only the 64 character subset [20<sub>16</sub>]

(space) to  $5F_{16}$  (\_)] and ignores all ASCII characters outside this subset with the exception of those characters defined as display commands. These display commands are shown in Figure 5. Displayed character sets for the HDSP-2470/-2471 systems are shown in Figure 6.

Figure 5. Display Commands for the HDSP-2470/-2471/-2472 Alphanumeric Display Controller.

<sup>\*</sup>DISPLAY COMMANDS WHEN USED IN LEFT ENTRY +DISPLAY COMMANDS WHEN USED IN RIGHT ENTRY

Figure 6. Display Font for the HDSP-2470 (64 Character ASCII Subset), and HDSP-2471 (128 Character ASCII Set) Alphanumeric Display Controller.

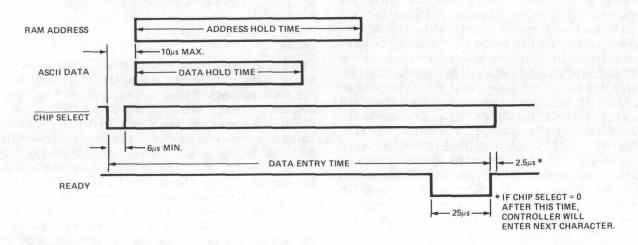

Regardless of whether a control word or ASCII data word is presented by the user, a READY signal is generated by the controller after the input word is processed. This READY signal goes low for  $25\mu s$  and upon a positive transition, a new CHIP SELECT may be accepted by the controller. Data Entry Timing is shown in Figure 7.

#### DATA ENTRY TIMING

#### MAXIMUM DATA ENTRY TIMES OVER OPERATING TEMPERATURE RANGE

| DATA ENTRY MODE       |        |           |               |               | F       | UNCTION          |         | ALC ELLE |

|-----------------------|--------|-----------|---------------|---------------|---------|------------------|---------|----------|

| HDSP-                 | DATA H | OLD TIME* | DATA<br>ENTRY | BACK<br>SPACE | CLEAR   | FORWARD<br>SPACE | DELETE  | INSERT   |

| LEFT (2471/2)         | 135μs  |           | 235μs         | 195μs         | 505μs   | 205μs            | 725µs   | 725µs    |

| LEFT (2470)           | 150μs  |           | 245µs         | 215µs         | 530μs   | 225μs            | 745µs   | 735µs    |

| RIGHT (2471/2)        | 85µs   |           | 480μs         | 470μs         | 465μs   |                  |         |          |

| RIGHT (2470)          | 105μs  |           | 490μs         | 490μs         | 485μs   |                  |         |          |

| RAM (2471/2)          | 55μs   | 120μs* •  | 190μs         |               |         |                  |         |          |

| RAM (2470)            | 55μs   | 130μs**   | 200μs         |               |         |                  |         |          |

| BLOCK (2471/2)        | 55μs   |           | 120µs         | (155μs F      | OR RIGH | TMOST CHA        | RACTER) |          |

| BLOCK (2470)          | 55μs   |           | 130µs         | (165μs F      | OR RIGH | TMOST CHA        | RACTER) |          |

| LOAD CONTROL (2471/2) | 50μs   |           | 505μs         |               |         |                  |         |          |

| LOAD CONTROL (2470)   | 50μs   |           | 505μs         |               |         |                  |         |          |

<sup>\*</sup>Minimum time that data inputs must remain valid after Chip Select goes low.

Figure 7. Data Entry Timing and Data Entry Times for the HDSP-2470/-2471/-2472 Alphanumeric Display Controller.

<sup>\*\*</sup>Minimum time that RAM address inputs must remain valid after Chip Select goes low.

#### **Left Entry Mode**

With Left entry, characters are entered in typewriter fashion, i.e., to the right of all previous characters. Left entry uses a blinking cursor to indicate the location where the next character is to be entered. CLEAR loads the display with spaces and resets the cursor to the leftmost display location. BACKSPACE and FORWARDSPACE move the cursor without changing the character string. Thus, the user can backspace to the character to be edited, enter a character and then forward space the cursor. The DELETE function deletes the displayed character at the cursor location and then shifts the character string following the cursor one location to the left to fill the void of the deleted character. The INSERT CHARACTER sets a flag inside the system that causes subsequent ASCII characters to be inserted to the left of the character at the cursor location. As new characters are entered, the cursor, the character at the cursor, and all characters to the right of the cursor are shifted one location to the right. The INSERT function is terminated by a second INSERT CHARACTER, or by BACKSPACE, FORWARDSPACE, CLEAR or DELETE. In Left entry mode, after the display is filled, the system ignores all characters except BACKSPACE and CLEAR. The system allows the cursor to be positioned only in the region between the leftmost display character and immediately to the right (offscreen) of the rightmost display character.

#### **Right Entry Mode**

In Right entry mode, characters are entered at the right hand side of the display and shifted to the left as new characters are entered. In this mode, the system stores 48 ASCII characters, although only the last characters entered are displayed. CLEAR loads the display with spaces. BACKSPACE shifts the display one location to the right, deleting the last character entered and displaying the next character in the 48 character buffer. Right entry mode is a simple means to implement the walking or "Times-Square" display. FORWARDSPACE, INSERT, and DELETE have character assignments in this mode since they are not treated as editing characters. In this mode, the cursor is located immediately to the right (offscreen) of the rightmost displayed character.

#### **Block Entry Mode**

Block entry allows the fastest data entry rate of all four modes. In this mode, characters are loaded from left to right as with Left entry. However, with Block entry, after the display is completely loaded, the next ASCII character is loaded in the leftmost display location, replacing the previous displayed character. While Block entry has a nonvisible cursor, the cursor is always loaded with the address of the next character to be entered. In this entry mode, the system can display the complete 128 character ASCII set. The display can be cleared and the cursor reset to the leftmost display location by loading in a new BLOCK control word.

#### **RAM Entry Mode**

In RAM entry, ASCII characters are loaded at the address specified by the five bit RAM address. Due to the limitation of only five address lines, RAM data entry is allowed only

for displays less than or equal to 32 characters. Regardless of display length, address 00 is the leftmost display character. Out of range RAM addresses are ignored. While RAM entry has a non-visible cursor, the cursor is always preloaded with the address to the right of the last character entered. This allows the cursor to be preloaded with an address prior to going into any other entry mode. In RAM entry, the system can display the complete 128 character ASCII set because it does not interpret any of the characters as control functions. The display can be cleared by loading in a new RAM control word.

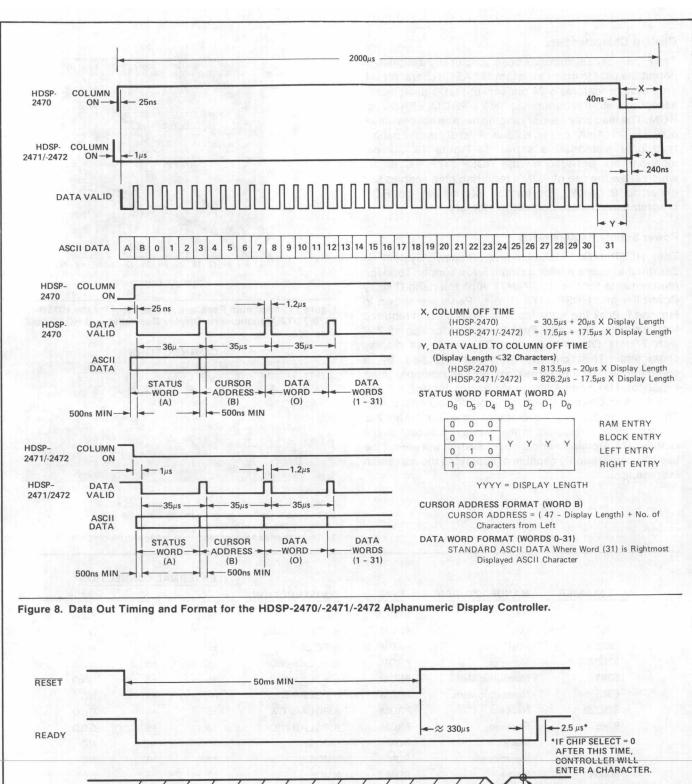

#### **Data Out**

For display lengths of 32 characters or less, the data stored in the internal RAM is available to the user during the time between display refresh cycles. The system outputs a STATUS WORD, CURSOR ADDRESS, and 32 ASCII data characters. The STATUS WORD specifies the data entry mode and the display length of the system. The STATUS WORD output differs slightly from the CONTROL WORD input. This difference is depicted in Figure 8. Regardless of display length, the CURSOR ADDRESS of the rightmost character location is address 47 (2F<sub>16</sub>) and the offscreen address of the cursor is address 48 (30<sub>16</sub>). The CURSOR ADDRESS of the leftmost location is defined as address 48 minus the display length. A general formula for CURSOR ADDRESS is:

#### CURSOR ADDRESS =

(47 - Display Length) + Number of Characters from Left.

For example, suppose the alphanumeric display is 16 characters long and the cursor was blinking at the third digit from the left. Then the CURSOR ADDRESS would be 47 - 16 + 3 or 34 (22<sub>16</sub>) and the 18th ASCII data word would correspond to the ASCII character at the location of the display cursor. In Left and Block entry, the CURSOR ADDRESS specifies the location where the next ASCII data character is to be entered. In RAM entry, the CURSOR ADDRESS specifies the location to the right of the last character entered. In Right entry, the CURSOR ADDRESS is always 48 (30<sub>16</sub>). The negative edge of the DATA VALID output can be used to load the 34 DATA OUT words into the user's system. The DATA OUT timing for the HDSP-247X systems are summarized in Figure 8. For displays longer than 32 characters, the system only outputs the STATUS WORD between refresh cycles.

#### Master/Power On Reset

When power is first applied to the system, the system clears the display and tests the state of the DATA INPUT, D7. If D7 > 2.0V, the systems loads the control word on the DATA INPUTS into the system. If D7  $\leq$  .8V or the system sees an invalid control word, the system initializes as Left entry for a 32 character display with a flashing cursor in the leftmost location. For POWER ON RESET to function properly, the power supply must turn on at a rate > 100 V/s. In addition, the system can be reset by pulling the RESET input low for a minimum of 50 milliseconds. POWER ON/MASTER RESET timing is shown in Figure 9.

READS IN CONTROL WORD DATA INPUT, D7 INITIALIZES AS LEFT ENTRY MODE, 32 CHARACTER DISPLAY LENGTH

Figure 9. Power-On/Master Reset Timing for the HDSP-2470/-2471/-2472 Alphanumeric Display Controller.

#### **Custom Character Sets**

The HDSP-2472 system has been specifically designed to permit the user to insert a custom 128 ASCII character set. This system features a 24 pin socket that is designed to accept a custom programmed 1K X 8 PROM, EPROM, or ROM. The read only memory should have an access time  $\leq 500_{ns}, \ l_{IL} \leq |\text{-.4mA}|$  and  $l_{IH} \leq 40\,\mu\text{A}$ . A list of pin compatible read only memories is shown in Figure 10. Jumper locations are provided on the HDSP-2472 P.C. board which allow the use of ROM's requiring chip enables tied either to 0 or 5V. For further information on ROM programming, please contact the factory.

#### **Power Supply Requirements**

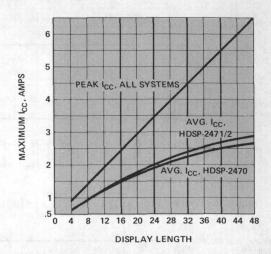

The HDSP-247X Alphanumeric Display System is designed to operate from a single 5 volt supply. Total Icc requirements for the HDSP-247X Alphanumeric Display Controller and HDSP-24XX Display Panel are shown in Figure 11. Peak Icc is the instantaneous current required for the system. Maximum Peak Icc occurs for Vcc = 5.25V with 7 dots ON in the same Column in all display characters. This current must be supplied by a combination of the power supply and supply filter capacitor. Maximum Average Icc occurs for Vcc = 5.25V with 21 dots ON per character in all display characters. The inclusion of a 375 X microfarad capacitor (where X is the number of characters in the display) adjacent to the HDSP-247X Alphanumeric Display System will permit the use of a power supply capable of supplying the maximum average Icc.

Figure 11. Maximum Peak and Average  $I_{CC}$  for the HDSP-2470/71/72 Alphanumeric Display Controller and HDSP-2000 Display.

#### CONNECTORS

| FUNCTION              | TYPE OF CONNECTOR             | SUGGESTED<br>MANUFACTURER                                                     |

|-----------------------|-------------------------------|-------------------------------------------------------------------------------|

| CONTROL/DATA<br>ENTRY | 26 Pin<br>Ribbon Cable        | 3M P/N 3399-X000 Series                                                       |

| POWER <sup>(1)</sup>  | 3 Pin<br>With Locking<br>Ramp | Molex P/N 09-50-3031 with 08-50-0106 Terminals                                |

| DISPLAY<br>DRIVE(2,3) | 17 Lead<br>Board to Board     | Amp P/N 1-530500-7, also available in board to cable and other configurations |

#### NOTES:

- (1) Power leads should be 18-20 gauge stranded wire.

- (2) The maximum lead length from the controller board to the display should not exceed 1 metre.

- (3) The suggested Amp connector is supplied with the controller.

| PART NUMBER | MANUFACTURER    | TYPE  | CONSTRUCTION | X   | <u>Y</u> | Z   |

|-------------|-----------------|-------|--------------|-----|----------|-----|

| 2758        | Intel           | EPROM | NMOS         | GND | GND      | +5  |

| 7608        | Harris          | PROM  | BIPOLAR-NiCr | NC  | NC       | NC  |

| 3628-4      | Intel           | PROM  | BIPOLAR-Si   | +5  | +5       | GND |

| 82S2708     | Signetics       | PROM  | BIPOLAR-NiCr | NC  | NC       | NC  |

| 6381        | Monolithic Mem. | PROM  | BIPOLAR-NiCr | +5  | +5       | GND |

| 6385        | Monolithic Mem. | PROM  | BIPOLAR-NiCr | NC  | NC       | NC  |

| 87S228      | National        | PROM  | BIPOLAR-TIW  | +5  | +5       | GND |

| 93451       | Fairchild ·     | PROM  | BIPOLAR-NiCr | +5  | +5       | GND |

| 68308       | Motorola        | ROM   | NMOS         | **  | NC       | NC  |

| 2607        | Signetics       | ROM   | NMOS         | * * | NC       | NC  |

| 30000       | Mostek          | ROM   | NMOS         | * * | +5       | NC  |

|             |                 |       |              |     |          |     |

<sup>\*</sup>Board jumpers correspond to pins 18, 19 & 21 of ROM.

**EXTERNAL CONNECTION\***

Figure 10. Pin Compatible 1K x 8 Read Only Memories for the HDSP-2472 Alphanumeric Display Controller.

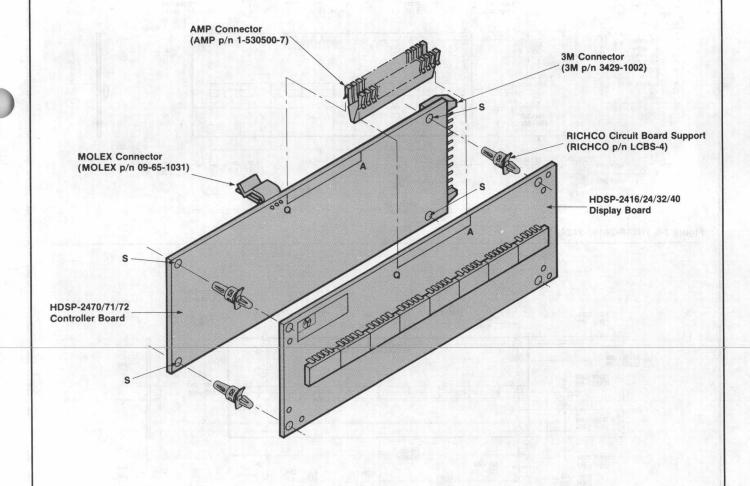

#### Display Boards/Hardware

The mechanical layout of the HDSP-247X Series allows direct mating of the controller P.C. board to a compatible series of display boards available from Hewlett-Packard. These display boards consist of matched and tested HDSP-2000 clusters soldered to a P.C. board.

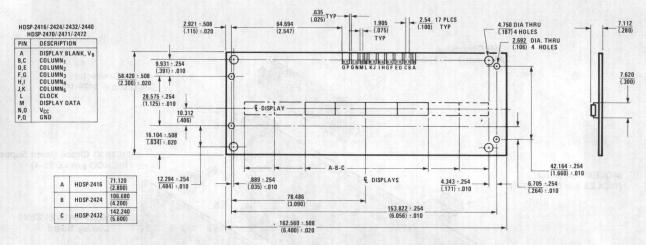

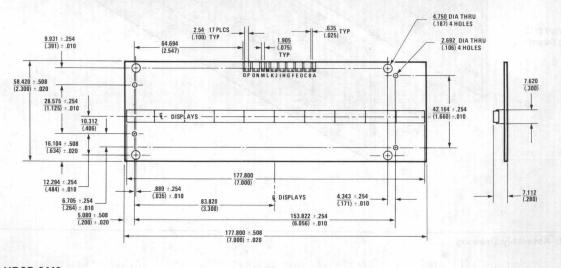

Included with the controller board are: 1 each Amp P/N 1-530500-7 board to board connector, and 4 each locking circuit board support nylon standoffs (Richco LCBS-4). This hardware allows the controller board to interconnect with any of the standard display boards. Figure 12 depicts correct assembly technique.

<sup>\*\*</sup> As defined by customer

#### **Assembly Steps**

- Insert the standoffs into .151 diameter holes (noted as "S" on Figure 12. The long end of the standoffs should protrude through the controller board side.

- 2. Position the controller board and display board with the components and displays facing out. The HP logo should be in the upper left corner when viewed facing the boards. Insert the standoffs through the mating holes on the display board and press the boards together so that the standoffs lock in place.

- 3. After the standoffs are secured, the Amp connector should be placed on the edge connect pads (marked "A" through "Q" Figure 12) at the top of the boards. Visual alignment of this connector may be done on the controller board by determining that the first connector contact finger is centered on the pad labeled "A".

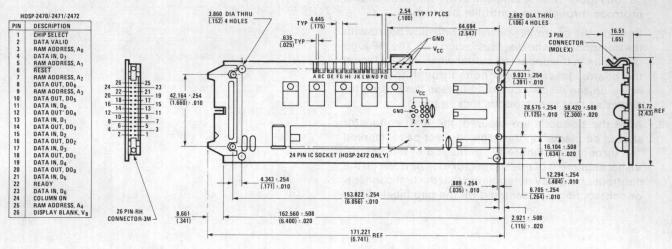

Figure 12. Assembly Drawing.

Figure 13. HDSP-2470/-2471/-2472

Figure 14. HDSP-2416/-2424/-2432

Figure 15. HDSP-2440