# JOURNAL

October 1995

## JOURNAL

#### Articles

| 6  | <b>HP PE/SolidDesigner: Dynamic Modeling for Three-Dimensional Computer-Aided Design</b> , by Klaus-Peter Fahlbusch and Thomas D. Roser |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 14 | User Interaction in HP PE/SolidDesigner, by Berthold Hug, Gerhard J.Walz, and Markus Kühl                                               |

| 24 | Enhancements in Blending Algorithms, by Stefan Freitag and Karsten Opitz                                                                |

| 35 | <b>Open Data Exchange with HP PE/SolidDesigner</b> , by Peter J. Schild, Wolfgang Klemm, Gerhard J. Walz, and Hermann J. Ruess          |

| 51 | <b>Providing CAD Object Management Services through a Base Class Library</b> , by Claus Brod and Max R. Kublin                          |

| 55 | Exception Handling and Development Support                                                                                              |

| 61 | Freeform Surface Modeling, by Michael Metzger and Sabine Eismann                                                                        |

| 69 | Common Lisp as an Embedded Extension Language, by Jens Kilian and Heinz-Peter Arndt                                                     |

| 74 | Boolean Set Operations with Solid Models, by Peter H. Ernst                                                                             |

| 78 | Fighting Inaccuracies: Using Perturbation to Make Boolean Operations Robust                                                             |

Executive Editor, Steve Beitler • Managing Editor, Charles L. Leath • Senior Editor, Richard P. Dolan • Assistant Editor, Robin Everest • Publication Production Manager, Susan E. Wright • Illustration, Renée D. Pighimi • Typography/Layout, John Nicoara

Advisory Board, Rajeav Badyal, Integrated Circuit Business Division, Fort Collins, Colorado - Thomas Beecher, Open Systems Software Division, Chelmstord, Massachusettes - Steven Brittenham, Disk Memory Division, Boise, Idaho - William W. Brown, Integrated Circuit Business Division, Santa Clara, California - Baeish Desai, Commercial Systems Division, Cupertino, California - Kevin G. Event, Integrated Systems Division, Sonnyale, California - Benhard Fischer, Böhlingen Medical Division, Böhlingen, Germany - Doruglas Genetten, Carelley Hardcopy Division, Freese Colorado - Gary Gordon, P.H. Zaboratones, Pende Alto, California - Mark Grumpki, Inkjet Supplies Business Unit, Corvallis, Oregon - Matt J. Harline, Systems Technology Division, Rosewille, California - Kivoyasu Hiwada, Hachioji Semiconductor Test Division, Tokyo, Jagan - Bryan Hoog, Lake Stevens Instrument Division, Everett, Washington - C. Steven Joiner, Optical Communication Division, San Jose, California -Reger L. Jungeriman, Microwave Technology Division, Santa Rosa, California - Streves Technology Division, Santa Rosa, California - Networked Systems Torusci. Longerta Division, Santa Rosa, California - Steven Joiner, Optical Communication Division, Santa Rosa, California - Networked Systems Torusci. Lovelant, California - Altred Maute, Waldbrinn Analytical Division, Waldbrinn, Germany - Andrew McLean, Enterprise Messaging Operation, Pinewood, England - Dona L. Miller, Workwide Customer Support Division, Mountair View California - Mitcheel IP. Moore, Wi Systems Division, Loveland, Colorado - Snelley I Moore, San Diego Printer Division, Son Diago, California - Mishaid Muttaba, HE Labaratories, Palo Altr, California - Steven J. Nanciso. VX Systems Division, Loveland, Colorado - Danny J. Oldfield, Electronic Measurements Division, Rolorado Springs, Colorado - Gatry Draolin, Software Technology Division, Roseville, California - Ham Tan, Mara Satatella, Software Engineering Systems Division, Palo Alto, California - Gunter Riebesell, Böblingen Instruments Divi

CHewlett-Packard Company 1995 Printed in U.S.A.

The Hewlett-Packard Journal is printed on recycled paper.

October 1995 Volume 46 • Number 5

Firmware Design for Wide-Bandwidth IF Support and Improved Measurement Speed

The HP 89400 Series Vector Signal Analyzers

An IF Module for Wide-Bandwidth Signals, by Robert J. Armantrout, Terrence R. Noe, Christopher E. Stewart, and Leonard M. Weber

The Log Weighted Average for Measuring Printer Throughput, by John J. Cassidy, Jr.

#### Departments

- 4 In this Issue

- 5 Cover

- 5 What's Ahead

- 107 Authors

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or include a business card) to the HP headquarters office in your country or to the HP address on the back cover. When submitting a change of address, please include your zip or postal code and a copy of your old label. Free subscriptions may not be available in all countries.

The Hewlett-Packard Journal is available online via the World-Wide Web (WWW) and can be viewed and printed with Mosaic. The uniform resource locator (URL) for the Hewlett-Packard Journal is http://www.hp.com/hpj/Journal.html.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1995 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice appears stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3000 Hanover Street, Palo Alto, CA 94304 U.S.A.

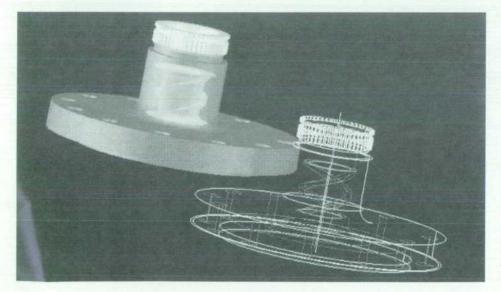

#### In this Issue

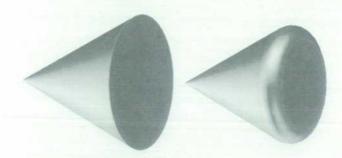

There's a good chance that many of the mechanical parts of the products you use, such as your car or your office printer, began their existence as solid models in a 3D computer-aided design (CAD) system. 3D solid modeling systems provide geometric models that can be translated into instructions for rapid part prototyping, injection moldmaking, or numerically controlled machine tool operation. Such systems, both commercially available and manufacturer-proprietary, are now undergoing rapid evolution, and mechanical designers are enjoying unprecedented and rapidly increasing productivity. However, most current systems are still history-based, meaning that if the designer doesn't have in-depth knowledge of the underlying solid modeling technology or doesn't thoroughly

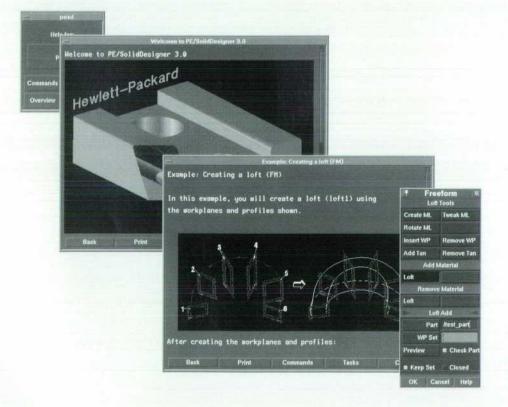

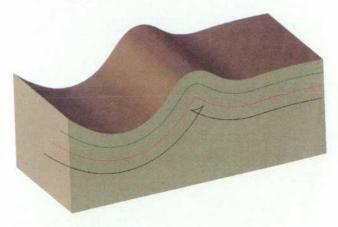

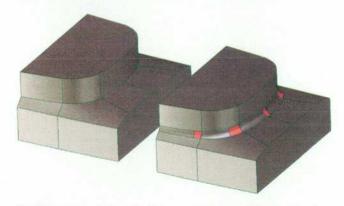

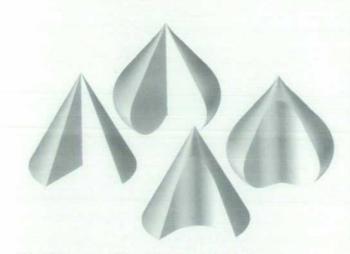

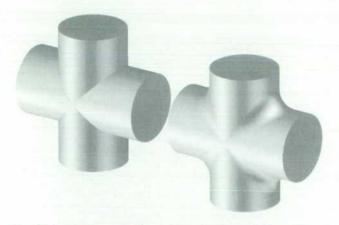

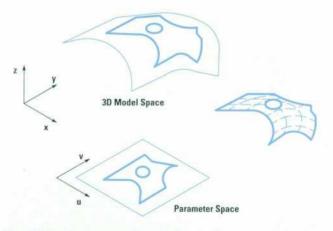

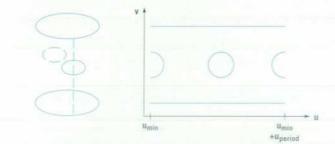

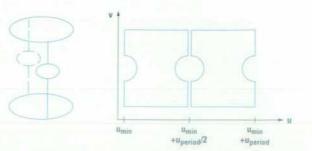

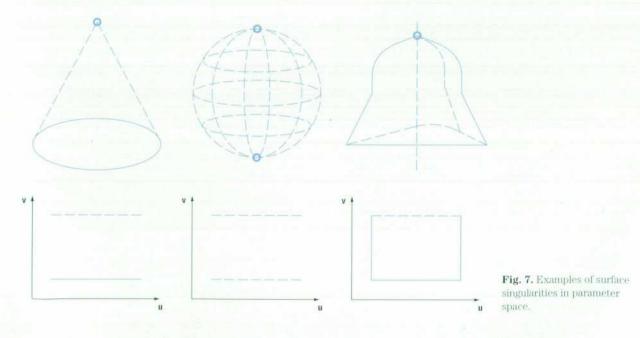

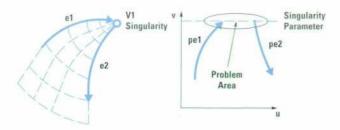

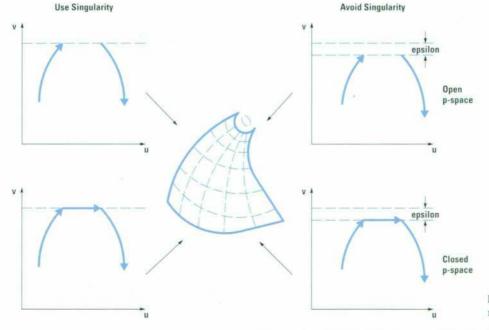

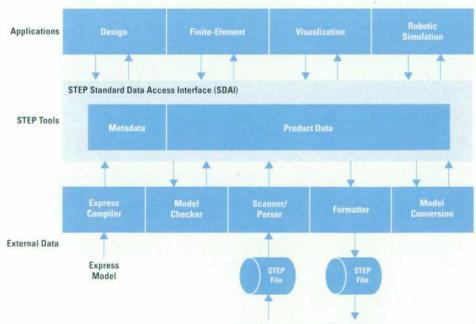

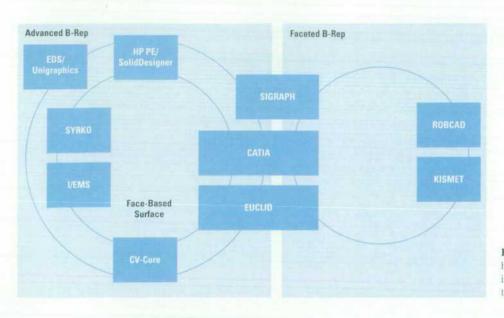

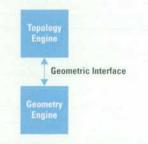

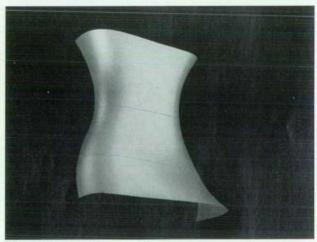

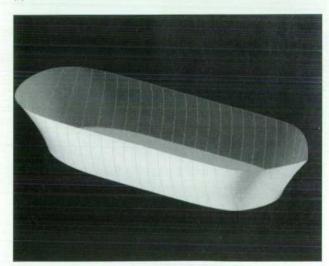

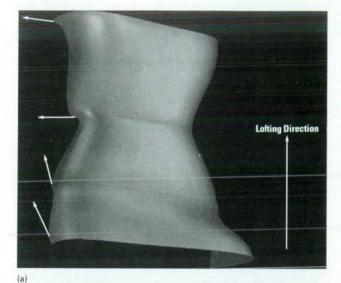

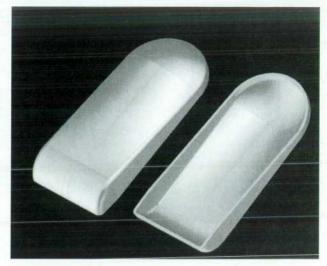

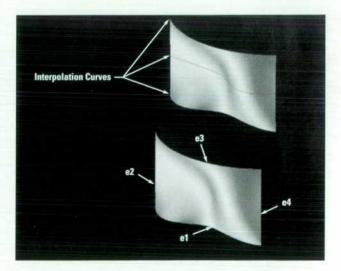

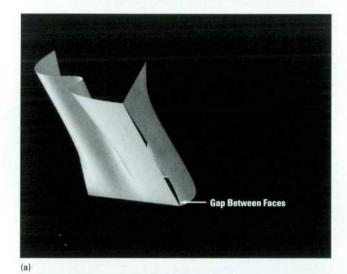

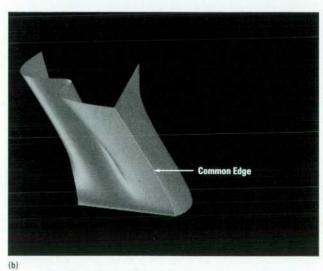

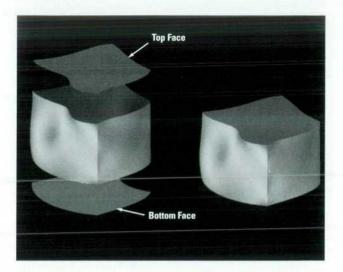

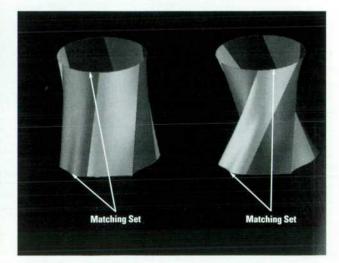

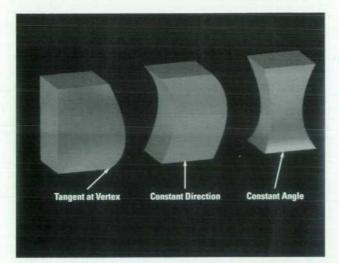

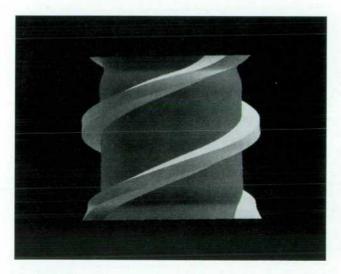

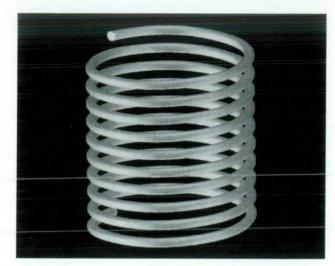

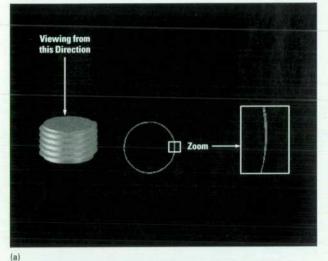

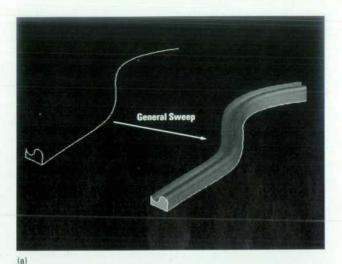

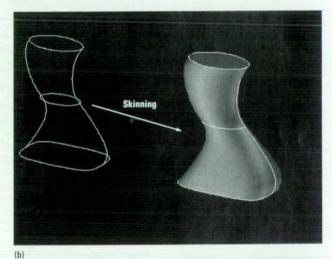

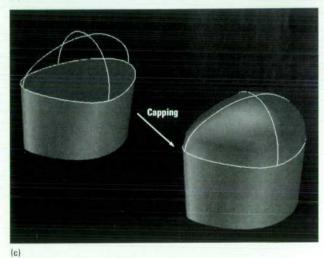

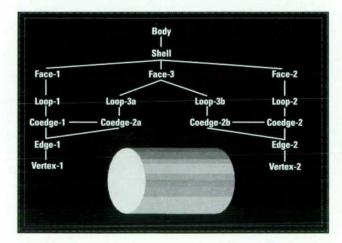

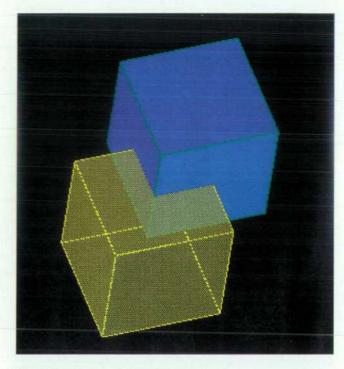

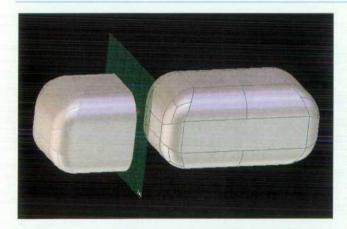

understand the history of the design, even seemingly trivial changes made to the model may have unanticipated side effects. In contrast, HP Precision Engineering SolidDesigner (PE/SolidDesigner) is an advanced 3D solid modeling CAD system based on dynamic modeling technology. As explained in the article on page 6, dynamic modeling removes any dependencies on history and eliminates the need to anticipate future changes, so that local geometry and topology changes can be made easily. When a change is made, a tool body is created and then transformed to the appropriate position. A Boolean operation between the original model and the tool body results in the desired change. The HP PE/Solid-Designer user interface (page 14) is designed to make the system easy to use for both experts and firsttime or occasional users. Internally, action routines representing commands interact with the user interface objects through a "personality"; this architecture makes it easy to change the user interface without changing the command syntax. To a computer, a 3D solid model is a highly complex data structure. HP PE/SolidDesigner's data structure manager (page 51), which has many of the characteristics of an object-oriented database, supports the data manipulation requirements of the solid modeling process, including the ability to slice the model into manageable packages that can be sent around the world, for example to subcontractors. Because HP business partners and customers may use other solid modeling systems instead of or in addition to HP PE/SolidDesigner, HP participates in international data exchange standardization efforts, most notably STEP, the Standard for the Exchange of Product Model Data. HP PE/SolidDesigner can import and export both surface and solid STEP data files. It can also import IGES (Initial Graphics Exchange Standard) surface and wireframe data files, and can import data files from its predecessor, the HP PE/ME30 3D CAD system. Data exchange is the subject of the article on page 35. Freeform surfaces are often needed in solid model creation, and HP PE/SolidDesigner provides two methods for creating them: blending, or edge rounding, and lofting. The article on page 24 describes the many subtleties of the sophisticated algorithm used for variable-radius blending. Complex combinations of convex and concave edges are blended predictably and reliably-a difficult design challenge. The article on page 61 tells how the product's geometric kernel implements lofting using a single-datatype geometric interface and a hybrid, multiple-data-type internal implementation. The lofting functionality features a clever analytic surface detection algorithm. The Boolean operations used to effect model modifications are implemented in the system's topology kernel, called the "Boolean engine." The article on page 74 explains the Boolean engine's complex algorithms in simple terms. Much of HP PE/ SolidDesigner is written in the Common Lisp programming language, which is also included in HP PE/ SolidDesigner as an extension and customization language for users (page 69).

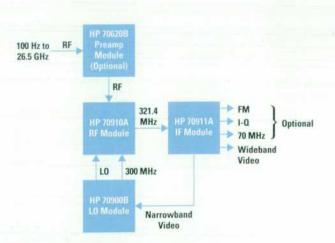

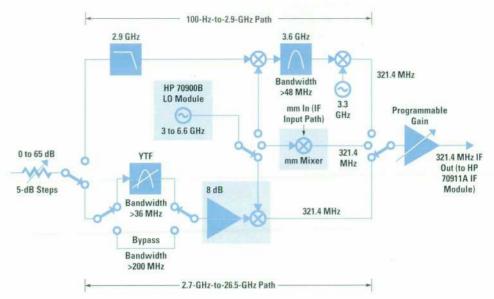

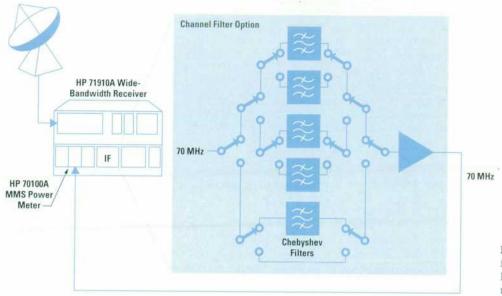

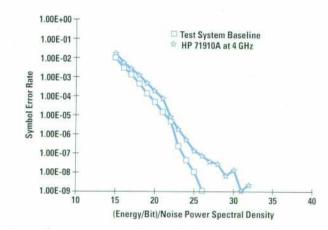

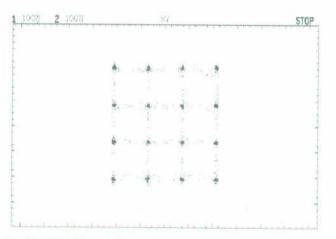

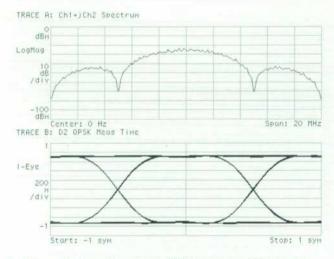

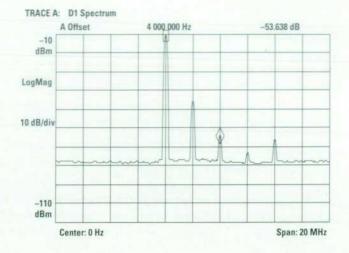

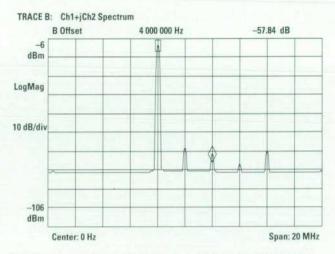

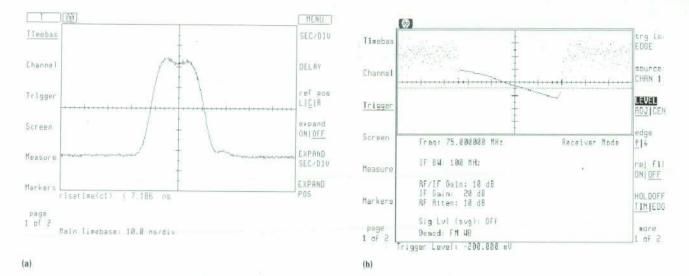

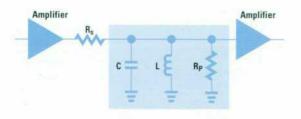

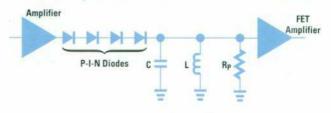

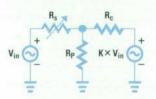

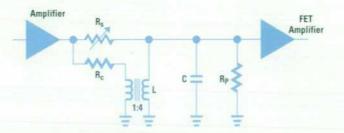

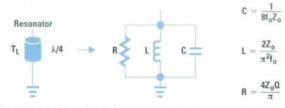

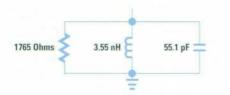

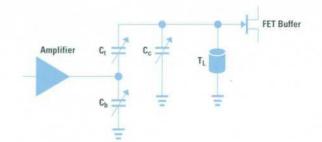

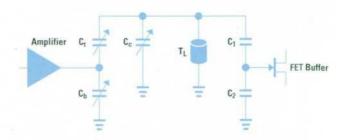

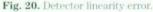

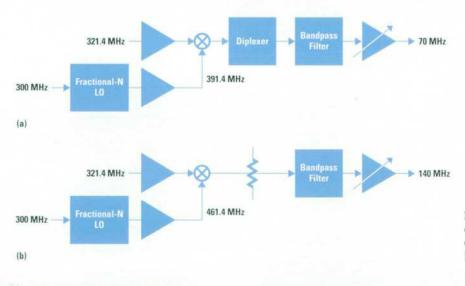

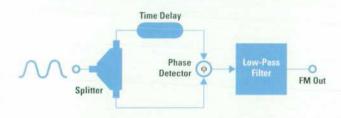

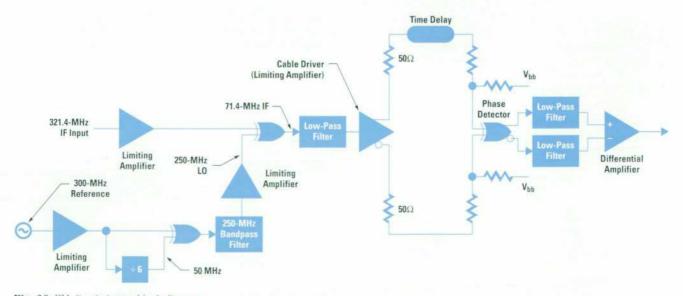

The microwave signals that ride our airwaves today are likely to have much wider bandwidths than those of yesterday. Spread spectrum techniques, increasingly used in radar systems and satellite and terrestrial communications systems, trade increased bandwidth for benefits such as increased noise immunity, lower power density, or increased security. The spectrum analyzers traditionally used to analyze microwave signals aren't up to the job of extracting all of the information from modern microwave signals because they don't have the bandwidth and don't reveal pulse, phase, or time-varying behavior. The HP 70910A wide-bandwidth receiver is designed to fill this need. It combines the attributes of a microwave spectrum analyzer, which include low internal noise, amplitude measurement accuracy, and wide frequency tuning with synthesizer accuracy and fine resolution. The HP 70910A wide-bandwidth receiver is the HP 70910A RF module and the HP 70911A IF module. The IF

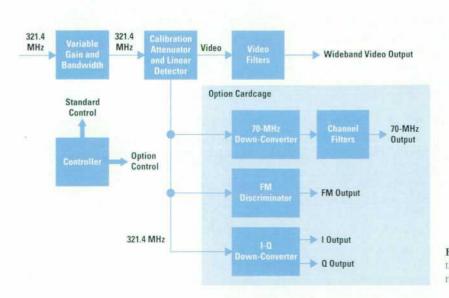

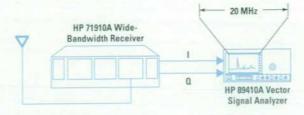

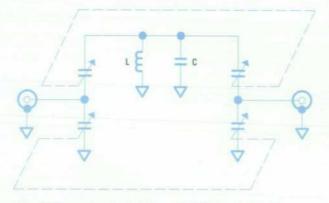

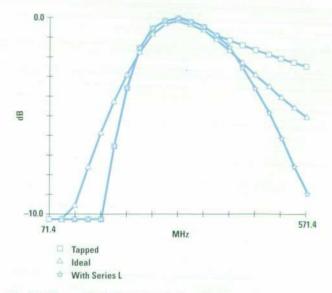

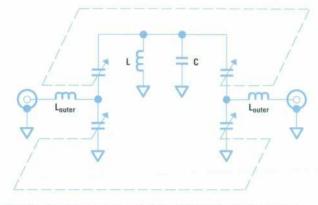

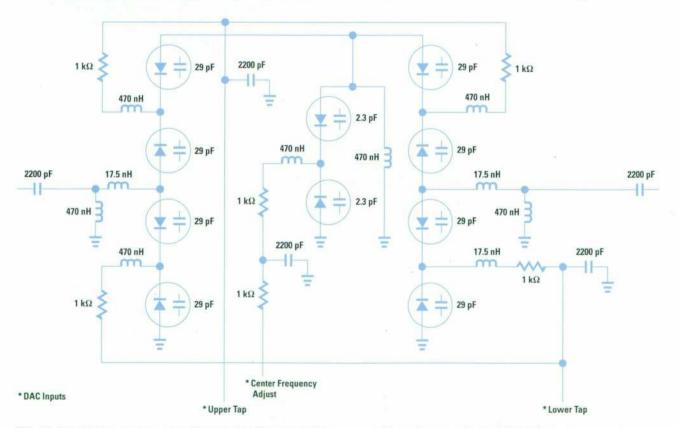

module provides the functions usually associated with a microwave receiver, such as intermediate frequency (IF) bandwidths from 10 to 100 MHz and pulse detection. It also offers options for FM demodulation, 70-megahertz IF output, and I-Q output (the type of modulation used in digital communications systems). The I-Q option can be used with a dual-channel vector signal analyzer such as the HP 89410A to extend the analyzer's bandwidth and frequency range. The two most common HP 70910A configurations operate over a frequency range of 100 hertz to 26.5 gigahertz. The design of the HP 70910A wide-bandwidth receiver and that of its RF module are described in the article on page 80. The IF module design, featuring variable-bandwidth, synchronous filters with tapped-capacitor, varactor-tuned resonators, is described in the article on page 89.

A color printer is typically used for a variety of documents, from simple black text pages that take a few seconds to print to color graphics pages that take several minutes. If you're the printer's designer, how do you measure how many pages per minute it will print so that you can judge the effects of design changes on a user's perception of its speed? The designers of the HP DeskJet 1600C printer considered the simple average and the simple weighted average, but rejected them in favor of the log weighted average. The article on page 104 tells why.

R.P. Dolan Senior Editor

#### Cover

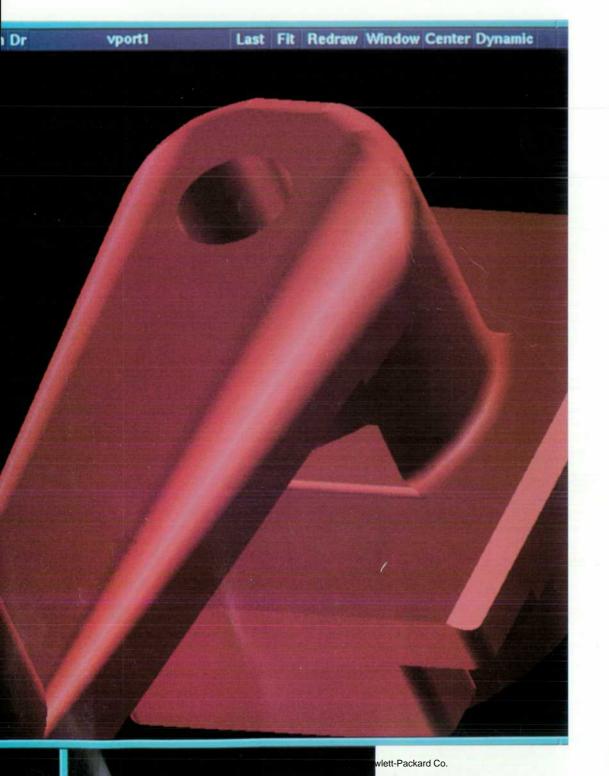

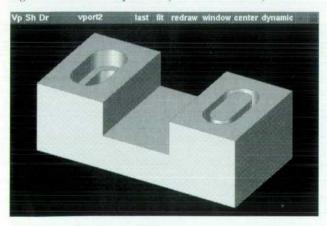

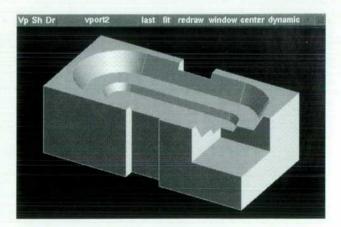

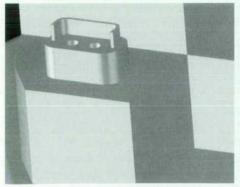

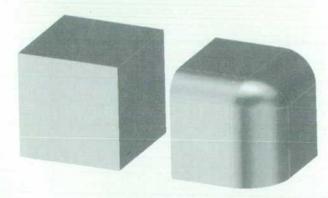

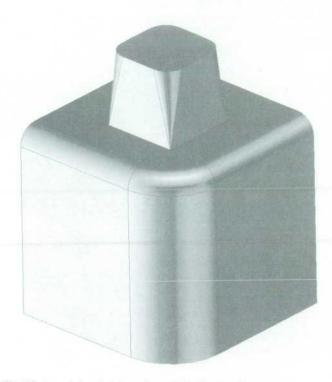

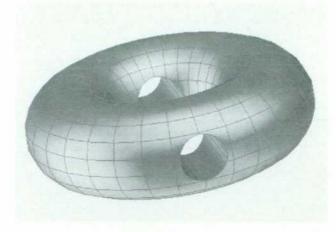

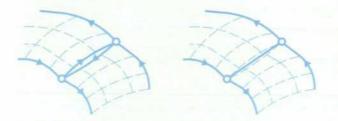

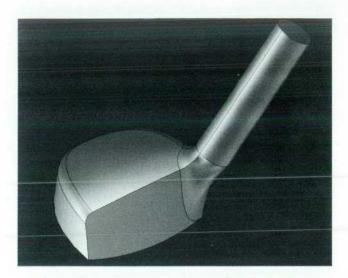

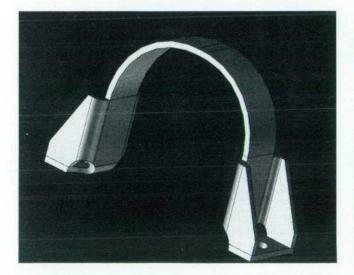

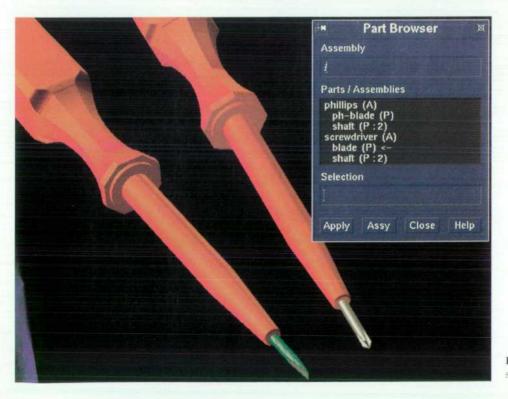

A solid model created and displayed using the HP Precision Engineering SolidDesigner 3D solid modeling system.

#### What's Ahead

The December issue will have ten articles on aspects of HP's implementation of the Open Software Foundation Distributed Computing Environment (OSF DCE). There will also be articles on the design of the HP Series 50 T fetal telemetry system and the HP HSMS-2850 zero bias diode for radio frequency identification applications.

## HP PE/SolidDesigner: Dynamic Modeling for Three-Dimensional Computer-Aided Design

In most solid modeling CAD systems, knowledge of the history of the design is necessary to avoid unanticipated side-effects when making changes. With dynamic modeling, local geometry and topology changes can be made independently of the model creation at any time, using both direct and dimension-driven methods. The core components enabling dynamic modifications are the tool body and the relation solver.

#### by Klaus-Peter Fahlbusch and Thomas D. Roser

HP Precision Engineering SolidDesigner (PE/SolidDesigner) is a 3D solid modeling design system based on the ACIS<sup>®</sup> Kernel (see "About Kernels" on next page). It provides the geometric model needed by design workgroups in product development environments. The system's dynamic modeling technology gives the designer the freedom to incorporate changes at any time and at any stage of product development, without dependence on the history of the product design.

HP PE/SolidDesigner is a member of the HP Precision Engineering Systems (PE/Systems) product family. Today, HP PE/Systems consists of:

- HP PE/SolidDesigner for solid modeling

- HP PE/ME10 for 2D design, drafting, and documentation

- HP PE/ME30 for 3D design

- HP PE/SurfaceStyler, an engineering styling application integrated with HP PE/SolidDesigner

- HP PE/SheetAdvisor, a sheet-metal design-for-manufacturability application

- HP PE/WorkManager for product data and workflow management

- HP PE/DDS-C for electrical system design

- HP PE/Complementary Application Program (CAP), a joint research and development and marketing program that provides HP PE/Systems users with access to more than 200 leading applications from 70 companies.

#### **HP PE/SolidDesigner**

HP PE/SolidDesigner makes it easy for designers to move to 3D solid modeling. It supports the coexistence of surface data with solid data and provides the ability to import and modify surface and solid design data from a variety of CAD systems. It also offers new modeling functionality and enhanced ease of use.

Using improved IGES (Initial Graphics Exchange Standard) import capability, both surface and wireframe data can be imported. Surface data and solid data can also be imported and exported using the STEP (Standard for the Exchange of Product Model Data) format. Once imported, this data can coexist with HP PE/SolidDesigner solid data. It can be loaded, saved, positioned, caught to (see footnote on page 15), managed as part and assembly structures, deleted, and used to create solids. Attributes such as color can be modified. If the set of surfaces is closed, HP PE/SolidDesigner will create a solid from those surfaces automatically. Other solid modeling systems, which are history-based, are unable to import data and then modify it as if it had been created within the system itself.

HP PE/SolidDesigner allows solid parts and assemblies to be exported to ACIS-based systems using Version 1.5 of the ACIS SAT file format. This feature provides a direct link to other ACIS-based applications.

With HP PE/SolidDesigner, users can set part and layout accuracy. Because users can model with parts of different accuracy by forcing them to a common accuracy, they can import and work on models from other CAD systems regardless of their accuracy.

Dynamic modeling is the underlying methodology within HP PE/SolidDesigner. This flexible, nonhistory-based, intuitive design technique provides direct interaction with modeling tools and designs, allowing the engineer to focus effectively on the design task.

HP PE/SolidDesigner allows designers to work with user-defined features to capture design intent. Users can explicitly group a variety of 3D elements such as faces and edges of a part. These features then can be viewed, edited, renamed, deleted, or used to drive changes to a design.

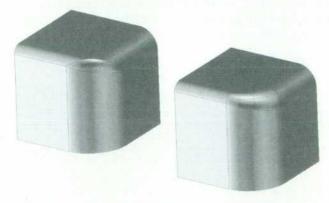

HP PE/SolidDesigner has variable radius blending, which allows users to create, modify, and remove variable blends. They can now create constant and variable blends during one session. Another new feature, called shelling, provides a quick way for users to create thin-walled parts from solids, as in injection-molded parts, for example.

Also new in HP PE/SolidDesigner is mass property capability. The following properties can be calculated for parts and assemblies: face area, volume, mass, center of gravity, inertia tensor, and boundary area. Tolerances can be supplied and achieved accuracies are returned. HP PE/SolidDesigner also incorporates interference-checking capabilities, which allow detection of interference, face touching, and noninterference of assemblies and part combinations. The results can be shown as text reports or in graphic format with color coding for easy identification.

About Kernels. A kernel is the heart of a modeling system. Currently, three kernels are used in various CAD systems. These are Romulus from Shape Data, Parasolid, an extension of Romulus, and the ACIS Kernel from Spatial Technology. The ACIS Kernel is rapidly becoming a de facto standard, having been accepted to date by 25 other commercial licensees, 50 academic institutions, and 12 strategic developers. As of July 1995, companies that officially have committed to using ACIS as their underlying technology include MacNeal-Schwendler/Aries, Applicon, Autodesk, Bentley Systems, CADCentre, Hewlett-Packard, Hitachi-Zosen Information Systems, Camax Manufacturing Technologies, Intergraph, and Straessle.

**About STEP**. The STEP protocol for data exchange is the product of a group of international organizations including PDES/PDES Inc. USA, a joint venture with several member companies, ESPRIT (European Strategic Program for Research and Development in Information Technology), European data exchange technology centers such as CADDETC (CADCAM Data Exchange Technical Centre) and GOSET, and ProSTEP, the German industry project for establishing STEP in the automotive industry.

HP has been active in STEP technology since 1989 through projects such as CADEX (CAD Geometry Exchange), PRO-DEX (Product Data Exchange), and ProSTEP. HP provides STEP processors with its HP PE/SolidDesigner 3D solid modeling software.

#### **Dynamic Modeling**

Currently, the most popular 3D CAD solutions are historybased. When designing with these systems, dimensions and parameters have to be specified at the outset. The model can only be manipulated indirectly by modifying these dimensions and parameters. The initial definitions have a major influence on the ease or difficulty of carrying out subsequent modifications, which can only be reliably implemented if all the previous steps in the design process are known. Laborious manipulation may be necessary to make changes that, intuitively, should be achievable in a single step.

Unless the history of the design is thoroughly understood, any change made to a model may have unanticipated sideeffects. Relatively straightforward changes to the model involve many convoluted steps. Future interpretation becomes ever more difficult and the effects of further modifications are unpredictable. Even when a single designer takes a part from start to finish, the designer will usually recreate the model from scratch many times as decisions made earlier make further progress impossible.

Although history-based systems are appropriate for solving family-of-parts problems, and are ideal for companies who simply produce variations on a given design, they are inflexible when used during the conceptualization phase of a project.

#### **Dynamic Modeling**

Dynamic modeling has been developed by HP to overcome the many problems designers experience with history-based CAD systems. In particular, it aims to remove any dependencies on history and the need to anticipate future changes.

The concept underlying dynamic modeling is to make optimal use of technologies without constraining the designer's creativity and flexibility. In contrast to history-based systems, dynamic modeling allows direct manipulation of model elements in 3D space. With dynamic modeling, local geometry and topology changes can be made independently of the model creation at any time, using both direct and dimension-driven methods. In the latter case, dimensions can be specified at any stage in the design, not just at the outset.

The core components enabling dynamic modifications are the tool body and the relation solver. To make a model modification a tool body is created and then transformed to the appropriate position. A Boolean operation between the original model and the tool body results in the desired model modification.

HP PE/SolidDesigner is the only currently available CAD solution that uses dynamic modeling. The remainder of this article describes the underlying technology of dynamic modeling and compares it with other methods like parametric model modification techniques.

#### State of the Art

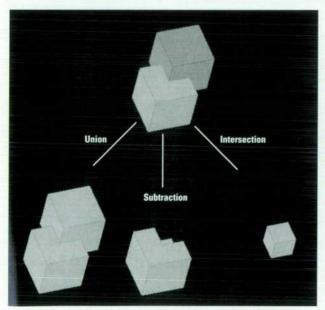

Currently, solid modelers use two different approaches to create the final geometrical model. CSG (constructive solid geometry) modelers are based on volume set operations with volume primitives such as cubes, cones, or cylinders. This approach is characterized by a Boolean engine, which implements the basic operators unite, subtract, and intersect. The sequence of all the Boolean operations, parameters, and positions of the primitives are kept in the CSG tree. Modification of the solid later in the design process can be done by using more primitives or by editing the CSG tree. Local modifications of the model are not possible, since no access to faces or edges is given. This cumbersome way to modify solids requires the user to analyze the design beforehand and dissect it into the necessary primitives and operations. While anticipating design modifications and building designs out of primitives is not typical in the mechanical engineering design process, pure Boolean modelers have proven useful when entering a final design for postprocessing, such as for finite-element analysis (FEM) or NC tool path programming.

B-Rep (boundary representation) modelers represent the solid by concatenating surfaces towards a closed volume. Model creation is similar to CSG modeling, but the user can work locally with surfaces, trim them against each other and "glue" them together. Local geometry modifications are very flexible and represent the way engineers think. For example, "I would like to blend this edge" is a natural way of specifying a model change for a mechanical engineer, while "I have to remove a volume that cuts away all material not needed" is a very unnatural way of specifying the same task during design.

As the development of B-Rep modelers continued, a new class of operations emerged in the early 1980s from the research institutes and appeared in commercial implementations. These operations are called *local operations*, or more commonly, *LOP*s, in contrast to global operations like Boolean set operations. Typical representatives of this kind of modeler are all Romulus-kernel-based systems like HP PE/ME30.

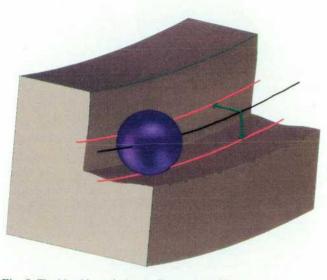

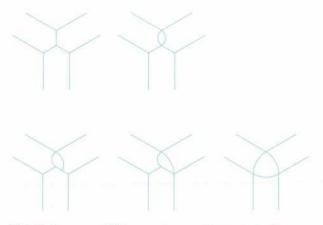

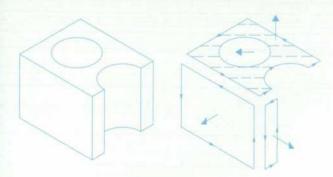

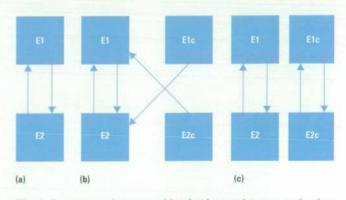

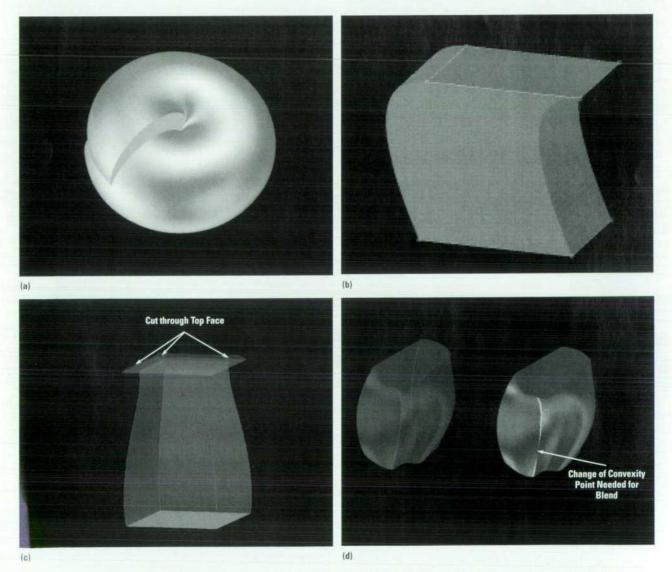

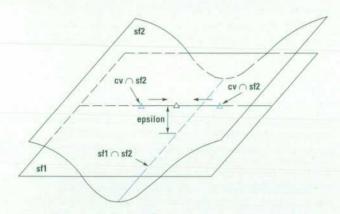

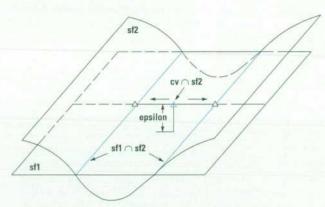

The difference between modifications with Boolean operations and modifications with LOPs lies in the amount of context analysis required. A Boolean operation always works on the complete volume of the operands (global operation). A LOP only analyzes the neighborhood of the operand and is usually not able to perform topological changes. To perform a model modification several constraints have to be met by the model, two of which are illustrated in Figs. 1 and 2.

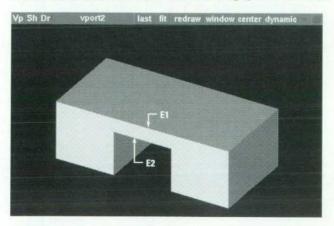

The example shown in Fig. 1 is a block with edge E1 to be blended (rounded). If the radius chosen for the blend is larger than the distance between the two edges E1 and E2, the topology of the model would need to be changed or the model would be corrupted.

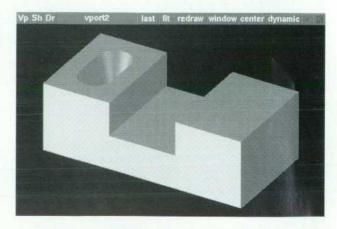

Fig. 2 shows a block with a pocket on its left side. To move or copy the pocket from the left top face to the right one cannot be done using LOPs, because both top faces would change their topology (i.e., add or remove faces or edges). The left top face would lose the inner loop resulting from the pocket while the right top face would add one.

These two restrictions are only examples of the complex set of constraints on the use of LOPs. Removing these restrictions one by one means evaluating more and more scenarios, thus adding to the complexity of the algorithms needed for the operations. A new approach was necessary.

#### The Tool Body

The limitations illustrated above led to the question, why can't Boolean set operations do the job? Boolean operations would be able to handle all special cases and at the same time would increase the stability of the algorithms. In the late 1980s a lot of research and development was done using this approach. Two directions were taken. The first was to further develop the old-style CSG modeling systems to make

Fig. 1. An example of the limitations of local operations (LOPs). Edge 1 is to be blended (rounded). If the radius chosen is larger than the distance between E1 and E2, the topology of the model must be changed or the model will be corrupted.

them easier to use. The second was to remove the limitations of LOPs in systems like HP PE/ME30 and all other Romulus-kernel-based systems. HP took the latter approach to develop the dynamic modeling capabilities of HP PE/-SolidDesigner.

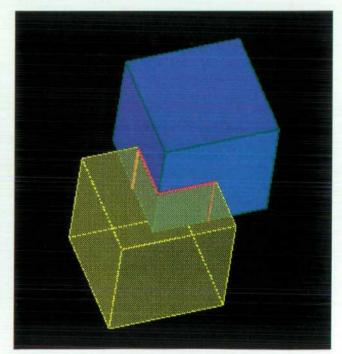

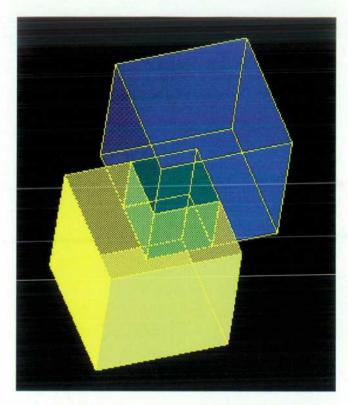

To enable model modifications with topology changes, Boolean operations were added to the LOP modification capabilities. The system generates a *tool body* and positions it according to the specifications of the modification. A Boolean operation between the original model and the tool body results in the desired model modification.

In this article, the term *basic local operations* (B-LOP) will be used for the normal LOP, which cannot perform topology changes, while the process of using the Boolean operation, if necessary or more appropriate, will be referred to as an *intelligent local operation* (I-LOP). Although the Boolean operation does not need to be done in all cases, the term I-LOP will be used to indicate that there can be a Booleanbased part of the operation.

To use the Boolean set operations for I-LOPs the system needs to create a tool body first. Two major approaches can be distinguished:

- Analysis of the the geometry to be modified and generation of an appropriate topological primitive (i.e., a basic volume element such as a cube, prism, or other) whose faces will be forced (tweaked) to build up the geometry of the tool body.

- Topological and geometrical creation of the tool body in only one step by analyzing the geometrical and topological neighborhood of the face to be moved.

The first approach is easier to implement if a utility function (a set of B-LOPs) is available that performs the task of tweaking a topologically similar object onto the required geometry of the tool body. The tweaking function, however, is tied to the restrictions of this utility function. The second method is more flexible but requires more knowledge about the internal structure of the CAD system's kernel.

We chose the first approach because HP PE/SolidDesigner already provided a working internal utility function for tweaking. The tool body generation for moving and tapering

Fig. 2. Another example of the limitations of LOPs. The pocket in the left top face cannot be copied or moved to the right top face using LOPs because both top faces would change topology by adding or removing faces and edges.

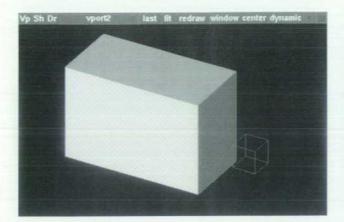

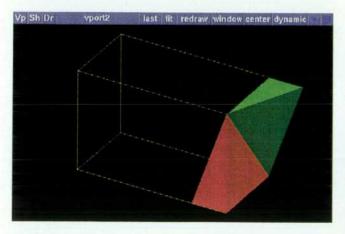

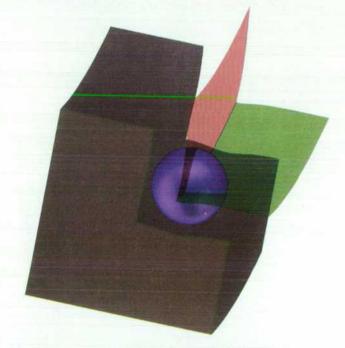

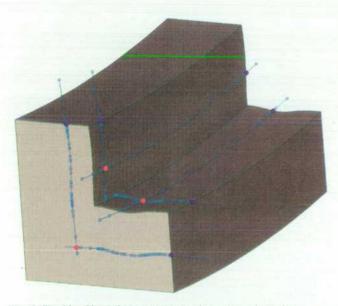

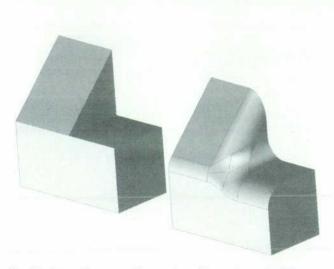

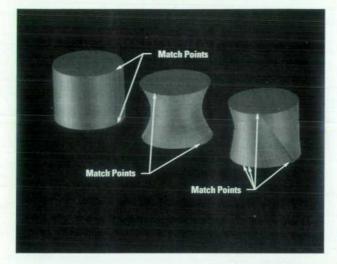

Fig. 3. The first step in the I-LOP (intelligent local operation) approach for a stretch (move face) operation in HP PE/Solid-Designer is the generation of the tool body, a four-sided prism in this case.

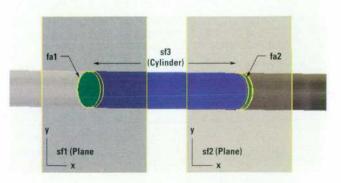

faces (and for bosses and pockets) follows two steps, which are carried out by the system automatically without any user intervention. First, a 3D body is created that has the topology of the final tool body. The part to be modified is analyzed to determine the topology of the 3D body that has to be generated for the requested operation. Depending on the number of edges in the peripheral loops of the face to be modified this body is either a cylinder (one edge), a half cylinder (two edges), or an n-sided prism, where n is the number of peripheral loops. Second, the geometry of this body is modified using basic local modifications. The result is the final tool body to be used for the model modification.

Figs. 3 to 5 illustrate this approach in further detail, showing the I-LOP approach for a stretch (move face) operation in HP PE/SolidDesigner. The user wants to stretch the box in Fig. 3, which means that the right face of the box will be moved to the right. The only and outer loop of the face to be moved contains four edges. Thus, the system creates a foursided prism in space at an arbitrary position.

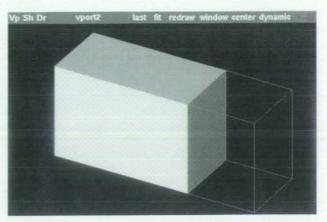

As shown in Fig. 4, the system then forces the faces of the prism onto the surfaces underneath the front, top, back, and bottom faces of the box (B-LOP). The left face of the prism will be forced onto the right face of the box and the right face of the prism will be forced into its final position, specified by the user.

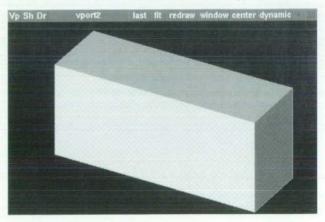

The last step, shown in Fig. 5, is the Boolean set operation (in this case a unite) of the tool body with the original 3D part, resulting in the modified 3D part. Although the modification in this example could have been achieved by employing a B-LOP operation, the use of the Boolean set operation will allow topological changes like interference of the stretched 3D part with some other section of the model.

The same approach works for faces with outer loops of nsided polygons. The curves describing the polygons are not restricted to straight lines. All types of curves bounding the face are valid, as long as the boundary of the face is convex. In cases of convex/concave edges special care has to be taken in tweaking the faces of the prism onto the geometry of the adjacent elements of the original part. An approach similar to the one described applies for tapering faces.

Fig. 4. The second step in stretching the box of Fig. 3 is to force the faces of the tool body to the final geometry, using a B-LOP (basic local operation).

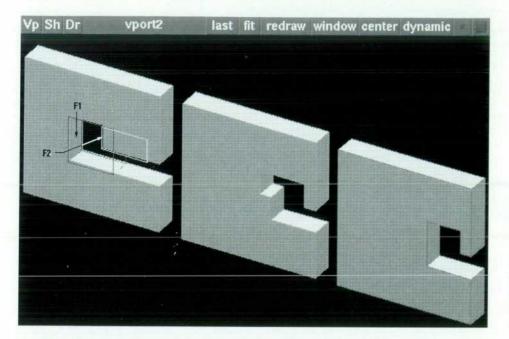

There is a high risk of getting unpredictable results or selfintersecting tool bodies when dealing with several faces that are not related to each other. Although the example in Fig. 6 may look somewhat artificial, it is characteristic of many possible situations. The user wants to move the two vertical faces F1 and F2 farther to the right, and expects a result as represented by the right part in Fig. 6. However, depending on the sequence of selection, two different results can be obtained.

If F2 is selected before F1, the I-LOP performs as expected and the result is as shown at the right in Fig. 6. If F1 is selected first, however, F1 will be moved first. The tool body belonging to F2 will then be subtracted from the body and will interfere with the final position of F1. This leads to the unexpected result shown in the middle of Fig. 6.

The conclusion is that only single faces can be modified and change topology during the modification. For multiple faces the I-LOP is too risky. If multiple faces are to be modified at once, basic local operations (B-LOPs) instead of Boolean operations will be activated. No topology change is allowed, of course. One major exception to this rule is the case of bosses and pockets, which will be discussed later.

Although in most cases the I-LOP approach will be applied, there are situations where self-intersecting tool bodies would be created and therefore the B-LOP approach is

Fig. 5. The final step in stretching the box of Fig. 3 is to unite the tool body and the original part, using a Boolean operation.

Fig. 6. Modification of several unrelated faces can lead to unanticipated results. Here the user wants to move faces F1 and F2 to change the part at the left into the part at the right. If F2 is selected before F1 the result is as expected, but if F1 is selected first the result is the part in the middle.

preferred even in cases with only one face to be moved. Fig. 7 shows such a situation. The user wants to rotate the right face around an axis lying in the face itself. Another likely situation would be aligning the right face with another face of the model.

Using an I-LOP in the way described above, a self-intersecting tool body would be created without special care to dissect the tool body into two tool bodies, one to add to the part and one to subtract from the part. In Fig. 7, the volume to be added is colored green and the volume to be removed is red. If HP PE/SolidDesigner detects a situation like this, a B-LOP is used for the modification.

### Geometry Selection and Automatic Feature Recognition

The next step in terms of increased complexity is the handling of groups of faces, which are known as bosses or pockets by mechanical engineers. These bosses and pockets need to be moved or copied, allowing topology changes. Of course the end user would appreciate it very much if these

Fig. 7. Here the user wants to rotate the right face around an axis lying in the face itself. This would create a self-intersecting tool body if an I-LOP were used. HP PE/SolidDesigner detects such situations and uses a B-LOP instead.

features could be selected as a unit as opposed to the cumbersome selection of faces sequentially.

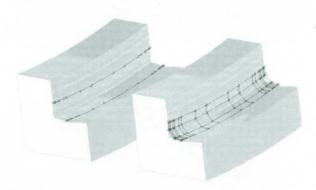

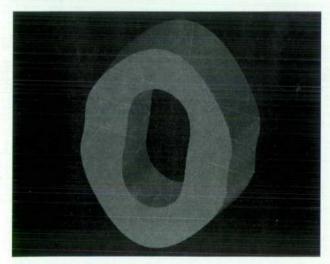

First, the terms boss and pocket need to be further specified. Bosses and pockets can be defined as a number of connected faces whose exterior boundary loops (the edges describing the intersection of the tool body with the original 3D part) are internal loops of a face. This definition is not easily conceivable and can be replaced by the more understandable, yet not very exact definition, "a number of connected faces contained in one or two nonadjacent others." This is easily conceivable by the end user and fits a lot of cases. Figs. 8 and 9 illustrate the copying of a pocket to which this definition applies.

For moving or copying bosses or pockets the system dissects the part along the edges that connect the boss or pocket with the remaining part. Both the tool body (the former boss or pocket) and the part to be modified now have open volumes (missing faces, or "wounds"), which are "healed" by the algorithm before further processing with the tool body.

Figs. 8 and 9 show only simple pockets. The question remains of how to deal with more complicated situations like

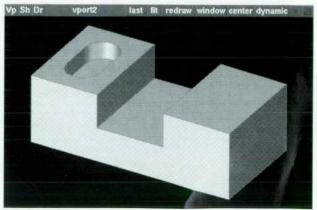

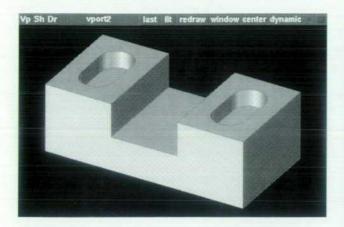

Fig. 8. A part with a pocket to be copied to the right top face.

Fig. 9. The part of Fig. 8 with two pockets, one copied. The system recognizes simple and compound bosses and pockets.

countersunk holes or bosses inside pockets. Fig. 10 shows the extension of the simple bosses and pockets. A boss or pocket containing countersunk bosses or pockets will be referred to as a *compound boss or pocket*. Any number of nested bosses or pockets is allowed, as shown in Fig. 10.

Simple and compound bosses and pockets are recognized by the system automatically, depending on the selection of the user. If one face within the boss or pocket is selected, the feature recognition algorithm identifies all other faces belonging to the selected boss or pocket.

Fig. 11 shows a part with a countersunk pocket. If the user selects one of the red faces in Fig. 11, the whole pocket is selected. If the user selects one of the yellow faces a smaller pocket will be recognized.

Feature recognition very much simplifies geometry selection. Instead of many picks to sample the list of faces for a move or copy operation, one single pick is enough. HP PE/ SolidDesigner recognizes the list of faces as a boss or pocket and the subsequent modification can include topological changes.

Once the bosses or pockets are selected, various I-LOPs are applied:

The "wound" in the top face of the part to be modified is healed, resulting in a simple block and a tool body consisting of the two nested pockets (the colored faces).

Fig. 11. Part with a countersunk pocket.

- This compound tool body is split into the larger pocket (colored red, nesting level 1) and a smaller pocket (yellow, level 2).

- Both tool bodies are transferred to their final positions.

- The larger tool body is subtracted from the block.

- The smaller tool body is subtracted from the result of the preceding, leading to the desired modification of the part.

The additional complexity of working with compound pockets or bosses is mainly handled by the Boolean engine of HP PE/SolidDesigner. Only a small part—the detection and subdivision of compound bosses or pockets—is needed in the I-LOP code itself.

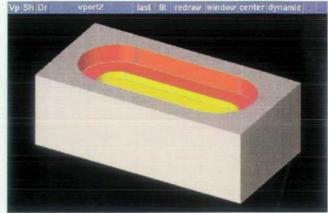

Fig. 12 shows the result of tapering a compound pocket with HP PE/SolidDesigner. (The front corner of the block has been cut away to show the tapered pocket.) If there were a need to change the topology by this operation, the Boolean operation inside the I-LOP would take care of it.

These features in PE/SolidDesigner don't have anything to do with the generation method of the model, as is the case in history and feature-based modelers. The features are defined temporarily for specific purposes; they are not part of the model. The flexibility of defining features at any stage in the design process is very much appreciated by most mechanical engineers.

Fig. 10. Part with one compound pocket and a boss inside a pocket.

Fig. 12. Part with a tapered, countersunk pocket. The front corner of the block has been cut away to show the tapered pocket.

Fig. 13. Part of an HP DeskJet printer printhead.

#### **3D** Labels for Dimension-Driven Modifications

In the past, if a mechanical engineer or draftsman had to adapt an existing design to new dimensions, the easiest way was to mark the dimensions as "not true in scale," erase the original value and put in the new value. The rest was left to the people on the shop floor.

This concept of modifying labels was adapted by CAD systems that use variational or parametric approaches in either 2D or 3D. The difference between the parametric and variational approaches is minor in this respect. Both systems require a completely constrained drawing or 3D model which is generated with the help of user constraints and system assumptions. New values of the dimensions cause a recomputation of the whole model. Any dependencies that the user might have specified are maintained even when the model becomes modified later in the design process. The design intent is captured in the model. While this approach is most efficient for family-of-parts designs, it does not support flexible modifications, which are needed in the typical iterative design process.

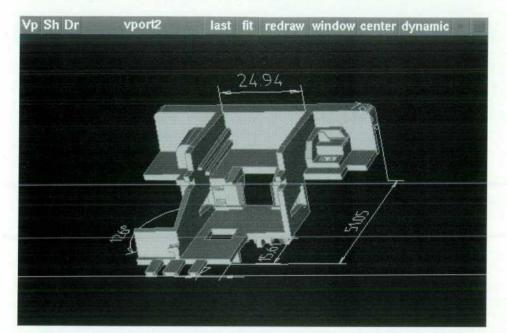

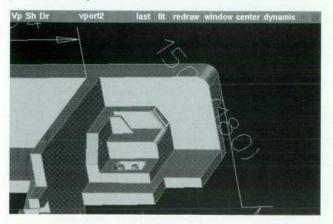

HP PE/SolidDesigner's dynamic modeling capabilities support the concept of 3D labels that can be attached to the

Fig. 14. Changing a dimension (the angle of the ramp) of the part of Fig. 13.

model at any time during the design process and can be used as *driving values*. Tapering of the selected geometry can be driven by angled labels, while the transformation of the selected geometry can be defined by employing distance labels. The user adds one or several 3D labels to the part, selects the geometry to be modified, and specifies new dimension values. Using the new values the system then performs the modification employing B-LOPs or I-LOPs. After the modification all values of the labels are updated to the current values of the geometry.

Fig. 13 shows the HP PE/SolidDesigner model of a part of the printhead of an HP DeskJet printer. Figs. 14 through 18 illustrate the concept of 3D labels.

As indicated in Fig. 14, the first draft of the design contained a 30-degree ramp that was to be used to aid manufacturing. All edges of the area are blended to meet casting requirements. Assume that later in the design process it turned out that the ramp was not needed at all or a different angle was needed. There are several ways to define the transformation in space for the ramp to disappear (e.g., aligning the original ramp face and the adjacent face below the ramp). If the user is trying to define the axis of rotation for the ramp face,

Fig. 15. The part of Fig. 13 with the new ramp angle (the ramp has been removed).

Fig. 16. The part of Fig. 13 changed by I-LOPs without the knowledge that there is a blended edge.

problems arise because the axis is a virtual one and cannot be found in the model. Either a special method for axis definition is needed or the user has to do the calculation by hand.

A third possibility is employing 3D labels. Using the 3D label already defined to show the functional angle enables the system to do all the necessary computation. A new value (in this example 180 degrees) needs to be entered by the user. The system derives the transformation that has to be applied to the ramp face and the model becomes updated. (Fig. 15).

If the label had not been ready for use, it could have been created to drive the modification. The labels are independent from the model creation and can be used temporarily. If the model has been changed, the values of the dimensions update automatically to their new values.

#### **Relation Solver**

Once the geometry to be modified is selected and new values of the labels are entered, the system will start with the unspecified transformation and six degrees of freedom (three translational and three rotational). The solver will derive the relations from the labels and reduce the number of degrees of freedom sequentially one after the other until all specified relationships are satisfied or an impossible configuration is encountered.

The system is only designed to solve relationships that can be described by equations solvable by algebraic means. No iterative solution is attempted.

Fig. 17. HP PE/SolidDesigner avoids the behavior of Fig. 16 by first suppressing the blend as shown here.

Fig. 18. After suppressing the blend, the system makes the change as shown here. The final step is to readd the blend as shown in Fig. 15.

The resulting transformation is dependent on the order in which the user has selected the modification-driving labels. Thus, the result of the modification is order dependent, especially if rotational and translational transformations are specified for the same modification.

#### **Modifying Blended Faces**

In Fig. 14, there are blends adjacent to the face to be moved. If the system didn't know that there were blends in the neighborhood of this face and how to handle them, moving the face might create a strange object like the one shown in Fig. 16.

To avoid this behavior, the system suppresses the blends in a preprocessing step before doing the main operation (rotate the ramp face) and recreates them after performing the main operation in a postprocessing step. Figs. 17 and 18 show the steps used by the system internally.

This concept adds to the flexibility of HP PE/SolidDesigner tremendously, because it overcomes the limitation of the B-LOPs that only modifications can be done that do not involve topological changes.

#### Summary

This paper shows the strengths of the dynamic modeling techniques. Topology changes are possible in most cases. Model modifications can be defined when they become required within the design process. Design changes do not have to be anticipated when starting the model creation. No constraints within the model exist, and predictable results avoid the trial-and-error approach of parametric and historybased systems. Dynamic modeling's core component besides the relation solver is the tool body, which is defined by the system automatically for the Boolean operation during a model modification. Although some limitations exist, most design changes are possible in one or several steps.

#### Acknowledgments

We would like to thank all those who helped with the development of dynamic modeling, in particular the Mechanical Design Division HP PE/SolidDesigner team, which was supported by 3D/Eye of Ithaca, New York and D-cubed of Cambridge, UK.

ACIS is a U.S. registered trademark of Spatial Technology, Inc.

## User Interaction in HP PE/SolidDesigner

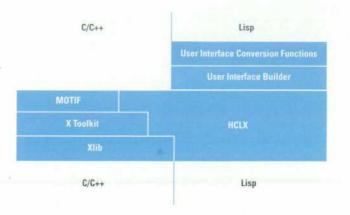

The HP PE/SolidDesigner user interface is modeled after the successful, easy-to-use, easy-to-learn interface of earlier HP CAD products. All commands are coded as Common Lisp action routines. A user interface builder helps command programmers by hiding details of the X Window System and the OSF/Motif<sup>™</sup> graphical user interface. Prototyping was done using a specially developed Lisp-based interface to OSF/Motif called HCLX.

#### by Berthold Hug, Gerhard J.Walz, and Markus Kühl

As the use of CAD systems has become more and more widespread, two conflicting trends have emerged. On one hand, the complexity of CAD systems has grown with their increasing functionality. On the other hand, the typical CAD system user is no longer a computer hobbyist. Designers and detailers are busy enough maintaining expertise in their own areas without having to be computer experts as well. Therefore, CAD software must be easy to learn and easy to use for first-time or occasional users without sacrificing flexibility and effectiveness for more experienced users. The conflict between the need for simple operation and the increasing functional complexity can lead not only to less user satisfaction, but also to decreased productivity. As a result, a simple and consistent user interface has been a long-standing goal of HP CAD products.

The user interface of HP PE/SolidDesigner is based on the successful user interface of HP PE/ME10 and PE/ME30. The key components of this user interface are:

- Ease of Use. The product is designed not only for experts, but also for first-time or occasional users.

- Menu Structure. A task-oriented, flat menu structure minimizes menu interaction and the length of cursor movements.

- Macro Language. This allows the user to customize the menu structure. User-defined functions can be set up to increase productivity by using existing CAD operations and measure/inquire tools for model interaction.

- Online Help System. This provides all relevant information to the user without using manuals.

The HP PE/SolidDesigner graphical user interface is based on OSF/Motif and the X Window System, universally accepted graphical user interface standards for applications software running on workstation computers. The OSF/Motif graphical user interface provides standards and tools to ensure consistency in appearance and behavior.

The large functionality built into HP PE/SolidDesigner is accessed by means of a command language with a defined syntax, referred to as *action routines*. The user communicates with the command language via the graphical user interface. All prompting, error checking, and graphical feedback are controlled by means of the command language. All CAD functionality is provided in this way, along with a user interface builder for implementing the graphical user interface.

The action routines are implemented in Common Lisp, which provides an easy and effective way of prototyping and implementing user interactions. For the first interactive prototypes, HCLX, a Lisp-based OSF/Motif interface, was used.

During the development of HP PE/SolidDesigner, HP mechanical engineers spend hundreds of days testing the product and providing feedback to tune its user interaction to meet their needs. They mercilessly complained about any awkward interactions. They made suggestions and drew pictures of how they would optimize the system for their particular tasks. As a result, commands were designed and redesigned to reflect their needs. The user interface verification was also supported by many external customer visits.

#### **User Interface Description**

If the user is familiar with other OSF/Motif-based applications, it's easy to feel comfortable with HP PE/SolidDesigner quickly. The mouse, the keyboard, and the knob box or spaceball are the tools for interaction.

When HP PE/SolidDesigner is started it looks like Fig. 1. The different areas are:

- Viewport (center of the screen). The viewport covers the main portion of the user interface and consists of the graphics area and the viewport control buttons at the top. In the graphics area of the viewport, the model is displayed and the user interacts with the model. Several viewports can exist, each with its own control buttons. Using more than one viewport, the user can view a part simultaneously from different sides and in different modes. Resizing and iconification of viewports are possible.

- Utility Area (top row). In the utility area, the user finds utility tools that support the current task. They do not terminate, but rather interrupt and support the current command. The help button at the right end gives access to the general help menu.

Fig. 1. Main screen of the HP PE/Solid Designer user interface.

- Main Menu (right side). The main menu buttons appear in the right column below the application name. This is also called the main task area. All the functionality is grouped into task-oriented logical areas. By selecting a main task button, the user opens a set of subtasks or a command dialog menu with buttons for all stages in the modeling sequence.

- Prompt Lines and General Entry Field (bottom left). The two-line prompt area is used for general system feedback, messages, or user guidance. The general entry field is used for entering commands, general expressions, and the like.

- Global Control Buttons (bottom right). The buttons at the bottom are always available. The select button is only active when the system is prompting the user to select something. The buttons and display fields inside the scrolled windows display general system settings like the active workplane or part, units, and catch information.<sup>+</sup> The other buttons are commands that the user needs frequently. They are always available.

Depending on the current command, the catch setting indicates how a pick in the graphics area (viewport) is processed to identify an element. For example, "catch vertex on current workplane" means that if the user picks near the end of a straight line, the resulting pick point will exactly match the endpoint of the line. The catch radius is customizable.

#### **Command and Option Dialogs**

Command dialog boxes (see Fig. 2) are accessed either from the main task area or the utility area. The current command dialog box is replaced by the new selected one. If the default home position of the command dialog box is inside the drawing area, the dialog box is closed upon completion of the operation (this is typical for command dialogs from the utility area). With this behavior the user always has optimal use of the screen space.

Nevertheless, sometimes the user wants to have parallel access to different dialog menus at the same time (flat structure). This can be achieved by pinning the command dialog to the screen using the small icon in the upper left corner. Pinned command dialog boxes are helpful whenever the user is using several menus constantly. The user can keep as many or as few dialog boxes open as desired and arrange them on the screen to suit the present task. Fig. 2 shows two pinned dialog boxes and one unpinned dialog box.

Activation of a command by a mouse click or by typing in a command in the general entry field leads to the same behavior. The command button snaps into pressed mode. If there exist a number of additional controls of the command, a

| Geometry Construct |             | <ul> <li>H Straight ⋈</li> <li>◆ Geometry ◇ Construct</li> </ul> |            | Ø <b>Ŧ Workplane</b> )<br>Create |              |

|--------------------|-------------|------------------------------------------------------------------|------------|----------------------------------|--------------|

|                    | ircle       | Line                                                             |            | New                              | Parallel     |

| Ctr & Rad          | Concentric  | 2 Pos                                                            |            | Сору                             | Inclined     |

| Fix Radius         | Fix Center  | Horizontal                                                       | Vertical   | Share                            | Last WP      |

| 3 Pos              | Diameter    | Parallel to                                                      | Perpend to | Mo                               | dify         |

| Tan & Cen          | Tan & 2 Pos | At an Angle                                                      | Ref Angle  | Position                         | Name         |

| Tan by 2           | Tan by 3    | Tangent to                                                       | Tan by 2   | Unshare                          | Owner        |

|                    | Arc         | Poly Lines                                                       |            | Settings                         | Slide Origin |

| Generic            | Concentric  | Polygon Rectangle                                                |            | Create New                       |              |

| Smooth             | Center      | OK Ca                                                            | ncel Help  | Name                             | w2į́         |

| 3 Pos              | Diameter    |                                                                  |            | Owner                            | 1            |

| Chang              | ge Circle   |                                                                  |            | Par to Face                      | Pt Pt Pt     |

| Radius             |             |                                                                  |            | Par to WP                        | Pt Dir       |

| OK Ca              | incel Help  |                                                                  |            | Norm to WP                       | Match Pts    |

|                    |             |                                                                  |            | /<br>⊴⊺                          |              |

|                    |             |                                                                  |            | Next                             |              |

|                    |             |                                                                  |            | OK Ca                            | ncel Help    |

Fig. 2. Command dialog boxes with pin icons in the upper left corner. Two boxes are pinned to the screen and one is not.

subdialog is attached at the bottom of the command dialog box (see extrude box in Fig. 3). The command becomes interactive and a prompt asks for further input. The dialog box gets a yellow border, a signal that this dialog box is active. If the action is suspended by an interrupt action, the border changes to red. Thus, the user never loses track of what is active and what is not.

The subdialog provides options in the form of buttons, data entry fields, and check boxes for further control of the command. The system provides good defaults to minimize the required user input. All options can be manipulated in any appropriate order; the command supplies a parallel syntax. All settings are displayed in the dialog box. Required data fields are highlighted in yellow, meaning that the user must define a value.

The help buttons of the command dialog boxes give access to context-sensitive help.

#### **Context-Sensitive Help**

Help messages relating directly to the task the user is performing can be accessed immediately by pressing the help button located in the currently active menu or dialog box. The help information appears in its own dialog box, which can be positioned anywhere on the screen and resized for convenience (see Fig. 4).

Words used in help text are directly linked to other definitions or explanations. The user need not go back to indexes to look up further words to aid in understanding the help information.

In addition to the context-sensitive help, the help system provides a task-based index with search facility, a commandbased index with search facility, an overview of HP PE/Solid-Designer, information on HP PE/SolidDesigner's concepts, filters, and displays of user-typed keywords, version information, and help on help. The help system can be used in a standalone mode without running HP PE/SolidDesigner.

#### Task-Sensitive Tools and Feedback

Whenever the user has to enter a value for a command, the system provides the appropriate tool for data entry. For instance, if the user has to enter a direction, the direction tool (Fig. 5) pops up. The user can extract the information directly out of the model with a minimum of effort by accessing parts of the model such as edges and faces. The result is displayed either textually or graphically as part of the model.

These task-sensitive tools are implemented as subactions so that all commands (action routines) have access to the same tools. Using these tools guarantees consistent system behavior, for example in specifying directions.

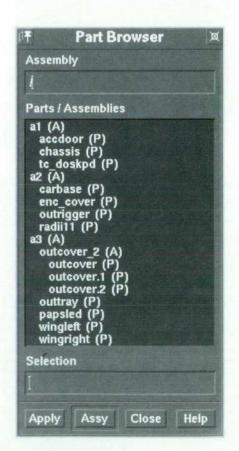

#### Browsers

Browsers (see Fig. 6) display lists of files, workplanes, parts, and assemblies, and allow selection of items for use in commands without typing in names. Even complex assemblies become easy to understand and manipulate when browsers are used.

#### Customizing the User Interface

HP PE/SolidDesigner provides different facilities for changing its user interface. The following customization capabilities exist:

- Flattening the Menu Structure. This facility is provided by allowing the user to pin command boxes to the screen.

When the environment is saved, pinning and location information is stored for later access.

- Toolbox. The toolbox (Fig. 7) allows the user to build a custom command dialog box. The user can put any command into the toolbox, and can put the most-used commands together in one area for easy access. The toolbox can be left open like a command dialog box. If a command becomes interactive, the original subdialogs are attached at the bottom of the toolbox dialog.

- Lisp. The user can write Lisp functions, which can contain action routine calls. Thus, the user can combine Lisp with CAD functionality to optimize the system for particular needs.

- Key Button Bindings. HP PE/SolidDesigner commands or Lisp functions can be accessed via X translations. Function keys, mouse buttons, or any key sequence can be defined for accessing any given functionality. This tool allows the expert user to accelerate the use of the system.

- Record/Playback. The record/playback feature allows the user to record a series of command picks to be used later to duplicate the action, like a macro. The information is stored in a file for playback. The file contains the command syntax, so it can be used to support writing user-defined Lisp functions.

#### Action Routines and Personality

This section describes the user interaction in HP PE/Solid-Designer in more detail. It explains the basic technology underlying the concepts that were described in the preceding section. A simplified extrude example is used to clarify the explanation.

Fig. 4. Context-sensitive help information appears in its own dialog box, which can be positioned anywhere on the screen and resized for convenience.

|                   | He Mea                              | isure 🕱                                                                                       |         |

|-------------------|-------------------------------------|-----------------------------------------------------------------------------------------------|---------|

|                   | Point 2D                            | Direction 3D                                                                                  |         |

|                   | Point 3D                            | Axis 3D                                                                                       |         |

| The second of the | Vector 3D                           | Angle                                                                                         |         |

|                   | Distance                            |                                                                                               |         |

|                   | Mass P                              | roperties                                                                                     |         |

|                   | Part & Assy                         | Face                                                                                          |         |

| TU                | Direction                           | 3D Output                                                                                     |         |

|                   | X: 0                                |                                                                                               |         |

|                   | Y: -0.01745<br>Z: 0.999847<br>OK Ca | G T Direct<br>X Y Z<br>Ref WP<br>U V W<br>Vp Dir<br>Face Normal<br>Two Points<br>Edge Tangent |         |

|                   |                                     | Accept                                                                                        | Reverse |

| 1                 |                                     | The Local State                                                                               | Hel     |

Fig. 5. When the user has to enter a value for a command, the system provides the appropriate tools for data entry. The result is displayed either textually or graphically as part of the model.

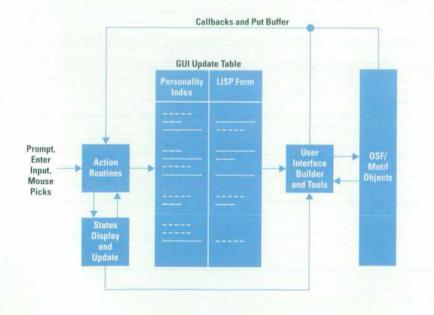

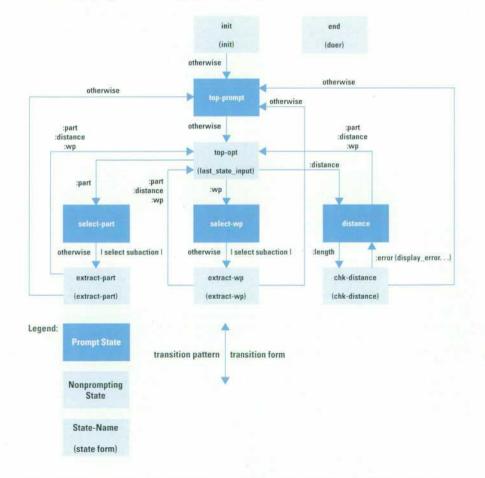

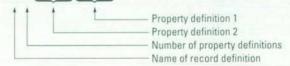

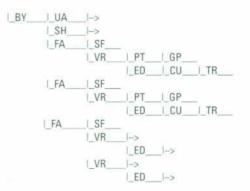

Fig. 8 is a simplified diagram of the action routine/personality communication model of HP PE/SolidDesigner. The communication model is divided into three parts. On the left side are the action routines and on the right side are the user interface objects. Bidirectional communication between the action routines and the user interface is the task of the *personality*, which is shown in the middle of Fig. 8. This division into three separate components allows the implementor of an HP PE/SolidDesigner command to change the user interface and its behavior without changing the command syntax. It is also possible to switch off the user interface for certain commands.

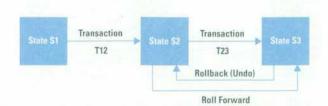

The action routine concept is used to implement the command language of HP PE/SolidDesigner. A command is coded as a state machine with several states and transitions between these states. The term personality refers to the information coded in the GUI update table shown in Fig. 8.

HP PE/SolidDesigner distinguishes three types of action routines:

- Terminate Actions. Terminate actions terminate every other running action routine *negatively* (i.e., they cancel them).

At any time there can only be one *active* or *suspended* terminate action. All action routines that modify the solid model must be defined as terminate actions.

- Interrupt Actions. Interrupt actions interrupt the current running action routine. When the interrupt action is finished, the interrupted (suspended) action routine continues from where it was interrupted. There is no limit on the stacking of interrupt actions. Interrupt actions must not modify the solid model. They are only allowed to inquire about model data. A measure command is an example of an interrupt action.

Fig. 6. Browsers make complex assemblies easy to understand and manipulate.

| Ling     | SolidDes    | signer       | The states |

|----------|-------------|--------------|------------|

| Viewport | Toolbox     | Measure      | WP-Browser |

|          | 👎 Too       | lbox 🛛       |            |

|          | Recorder    | C-line V     |            |

|          | Reset       | WPL by face  |            |

|          | Start ME10  | Extrude      |            |

|          | C-line H    | Move face    | 1          |

|          | Extr        | rude         | -          |

|          | Part        | <i>i</i> p1  | -          |

|          | Workplane   | <i>i</i> w1] | -          |

|          | ♦ Distance  | Insered a    |            |

|          | To Part     | 1            |            |

|          | Reverse Dir |              |            |

|          | ■ Keep WP   |              |            |

|          | OK Car      | ncel Help    |            |

Fig. 7. The toolbox allows the user to build a custom command dialog box containing often-used commands.

• Subactions. Subactions are used to implement frequently used menus so that they can be reused in other action routines. This avoids code duplication, allows better maintenance, and improves usability. Subactions can only be called from within other action routines. This means that the user cannot call a subaction directly. Some typical examples of subactions are:

• Select

- <sup>o</sup> Measure axis, direction, point

- Color editor

- Part positioning.

#### **Basic Action Routine Structure**

As mentioned above, the user interface in HP PE/SolidDesigner is Lisp-based. Therefore, the implementation of an HP PE/SolidDesigner command using the action routine concept is a kind of Lisp programming. The following is a schematic representation of a terminate action:

(defaction name

() ;; List of local variables (with or without initialization)

( ;; action description

(state\_form) (state\_prompt)

help-index-symbol

(transitionpattern (transition\_form) pers-update-symbol next\_state

... ;; more transitions

) ....:: more states

) ;; end of action description

(;; local functions

(local-fun ()

)

... ;; more local functions

) ;; end of local function definitions

The structure of an interrupt action or subaction is equivalent to that of the terminate action shown above except that an interrupt action is defined using the keyword defiaction and a subaction is defined using the keyword defiaction. The second parameter of the action routine definition is the

Fig. 8. In the HP PE/SolidDesigner user interface communication model, the action routines representing the commands communicate with the user interface objects through the personality. name of the command that is coded through the action routine. For an extrude command this would be extrude. Following the command name is a list of local action variables. These variables can only be accessed from within this action routine. Action routine local functions and each state and transition form have access to them. They are used to store user-entered command parameters and as variables to control the execution of the command.

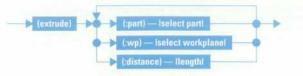

Next comes a description of the state machine. The states are those defined by the *railroad* of the command plus internal administrative states. The railroad of a command is a structure used to describe the syntax of an HP PE/SolidDesigner command for the user. Fig. 9 shows the simplified railroad of the extrude command (a few options have been omitted for clarity). The railroad reflects the concept of parallel command syntax. Each keyword (:part, :wp, :distance) can be given at any time and the command loops until the user completes or cancels it.

A distinction is made between prompting and nonprompting states. A prompting or prompt state requires the input of a token (a keyword or parameter value) from the user. This token is read from the input stream, which is filled either interactively by the user (hitting an option button, entering a number, selecting a part, etc.) or from a file (such as the recorder file). As many tokens as desired can be entered into the input buffer. Entered tokens are processed by the action routine handler. Processing stops as soon as an error occurs (such as an unknown keyword) or the input buffer becomes empty. HP PE/SolidDesigner then becomes interactive and requires more input from the user. A prompt state with an empty input buffer displays the prompt coded in its

Fig. 9. Simplified railroad giving the high-level syntax of the extrude command.

state. After the user has entered a token, the action routine handler tries to match the input with one of the state transitions. If a match is found the action routine handler processes this transition and jumps to the next state. A nonprompting state (administrative state) takes the result of its state form to find a match with the coded transitions of this state. If the action routine handler was not able to find a match in the transitions and no "otherwise" transition was coded, it signals an invalid input error.

Implementation of the extrude railroad leads to the state machine shown in Fig. 10. As the extrude command starts, the first state is init. In this state the local variables are initialized and filled with useful defaults such as the current part and the current workplane with a valid profile. Since init is a nonprompting state and only one "otherwise" transition is coded the action routine handler goes on to the next state, top-prompt. This prompt state and the nonprompting dispatch state top-opt are the central states of this example command. The top-opt state takes the input of the previous state (topprompt or any extract or check state) and tries to match its transitions. The states select-part and select-wp call on their only "otherwise" transition, the select subaction, as their transition form, with the specific select focus of part or

Fig. 10. State machine for the extrude command.

workplane, respectively. These states prompt through the select subaction. The extract states take the result of the transition form (select subaction call) and process the result of the select operation. The distance state has a special keyword—length—as its transition pattern. For this keyword an input conversion is involved. The transition pattern will match any entered number, whereupon a units converter will be called automatically. A user can work in length units of millimeters or inches, and the units converter converts the length into the internal units (here mm). There are also other converters such as the angle converter which converts the user input (e.g., degrees) into internal units (here radians).

The extrude command loops until the user completes or cancels the command. In both cases the action routine handler jumps into the separated state end. Depending on a positive (complete) or negative (cancel) termination of the command, the software that actually performs the action will be called with the parameters that were collected by the action routine.

#### Personality

As explained earlier, the task of the personality is bidirectional communication between the action routine and the user interface objects. The core of the personality is the GUI update table shown in Fig. 8. This table stores all of the actions to be performed when an action routine executes, and it also receives data from the user. It guarantees that the user interface is in sync with the action routine state whenever HP PE/SolidDesigner requires data from the user.

The GUI update table is realized as a hash table with the pers-update-symbol (see action routine representation, page 19) as key and a Lisp form as entry. As soon as the action routine handler finds a match in the transition pattern of the current state it performs the transition form and triggers the user interface update using the third parameter of the transition definition as value. The action routine handler looks up whether a Lisp form is coded for the pers-update-symbol and evaluates it if found. The Lisp form can contain things like set-toggle of a command option or update-toggle-data to show the value the user has entered. This mechanism reflects the state of the action routine and its values at any time in the user interface.

There are special personality keywords for every action routine:

- action\_name\_ENTRY

- 'action\_name\_EXIT

- '(action\_name action-interrupt-by-iaction)

- '(action\_name action-continue-from-iaction).

'action\_name\_ENTRY is triggered as soon as the action routine starts. Normally the Lisp form coded for this entry ensures the display of the command options filled with all default values. 'action\_name\_EXIT cleans up the user interface for this command and removes the options from the screen. The other two keys are triggered when the command is interrupted or when it resumes its work after an interrupt action. In this case the coded Lisp form normally deactivates and reactivates the command options, since they are not valid for the interrupt action.

**Delayed Update.** A sequence of action routine calls (e.g., from the recorder file) or the input of several tokens into the

input buffer should not cause constant updating of the user interface. Delayed update means that the user interface will not keep track of the action routine until the action routine becomes interactive, that is, until it requires data input from the user. At that time the user interface of the interactive command will reflect its state and values exactly.

A completely parameterized action routine does not cause any reaction on the user interface. If a command changes any status information (e.g., current part), this information will be updated. These updates bypass the GUI update table using the event mechanism.

The delayed update mechanism is implemented using a *personality entry stack*. Each trigger of a pers-update-symbol through the action routine handler will not lead to a direct execution of the Lisp form. All triggers are kept on the personality entry stack until the action routine becomes interactive. If an action routine doesn't require data from the user, all entries between and including ' action\_name\_ENTRY and ' action\_name\_EXIT are removed from the stack. As an action routine becomes interactive all Lisp forms belonging to the personality entries on the stack are performed until the stack is empty. The user interface is again in sync with the action routine state.

A problem came up with fully parameterized action routines behind a command toggle. Normally the 'action\_name\_EXIT trigger cleans up the command user interface, but with a fully parameterized action routine no personality trigger occurs. To solve this problem the system triggers two additional personality entries which are called in either delayed or undelayed update mode. These are 'action\_name\_PRE\_ENTRY and 'action\_name\_POST\_EXIT. The release of the command toggle is coded in 'action\_name\_POST\_EXIT. The need for 'action\_name\_PRE\_ENTRY is discussed below.

**Personality Context**. One requirement for the user interface of HP PE/SolidDesigner was that a command should be callable from other locations as well as from the default location. The motivation was the toolbox, which can be filled by the user with often-used commands. The main requirement was that a command's behavior in another context should be equivalent to its behavior in the default context. A user who calls the extrude command out of the toolbox expects the extrude options in the toolbox and not those in the default menu. The toolbox concept is based on the assumption that a command context is specified by:

- A calling button

- A dialog shell, in which the calling button resides

- A communication form where the command options are shown

- A shell position where the command options are shown if they are realized in a separate dialog shell.

All other things are command-specific and independent of the context.

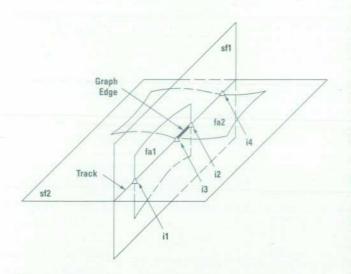

The default context of a command is coded in 'action\_name\_PRE\_ENTRY. Here the programmer of the command's personality defines the context in which the command should awake as the user types it in. This context can be overridden when the command is called out of, for example, the toolbox. Context dependent calls of the command personality have to check the current context settings instead of having this behavior hardcoded in the default context. This concept also makes it possible to program a totally different personality for a command or to switch off the user interface of a command.