# JOURNAL

August 1994

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or include a business card) to the HP headquarters office in your country or to the HP address on the back cover. When submitting a change of address, please include your zip or postal code and a copy of your old label. Free subscriptions may not be available in all countries.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1994 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3000 Hanover Street, Palo Alto, CA 94304 U.S.A.

## JOURNAL

#### Articles

| 6  | An Advanced Scientific Graphing Calculator, by Diana K. Byrne, Charles M. Patton,<br>David Arnett, Ted W. Beers, and Paul J. McClellan     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 20 | User Versions of Interface Tools                                                                                                           |

| 23 | HP-PAC: A New Chassis and Housing Concept for Electronic Equipment, by Johannes Mahn,<br>Jürgen Häberle, Siegfried Kopp, and Tim Schwegler |

| 29 | High-Speed Digital Transmitter Characterization Using Eye Diagram Analysis, by Christopher M. Miller                                       |

| 38 | Thermal Management in Supercritical Fluid Chromatography, by Connie Nathan and Barbara A. Hackbarth                                        |

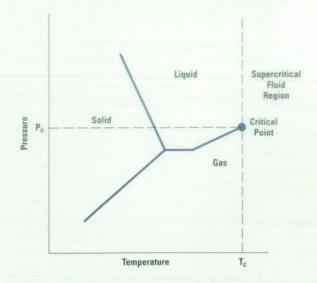

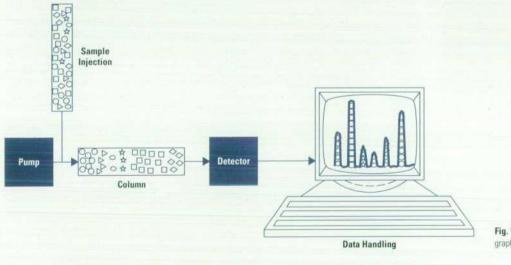

| 39 | What is SFC?                                                                                                                               |

| 43 | Linear Array Transducers with Improved Image Quality for Vascular Ultrasonic Imaging,<br>by Matthew G. Mooney and Martha Grewe Wilson      |

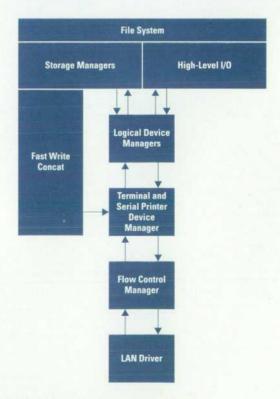

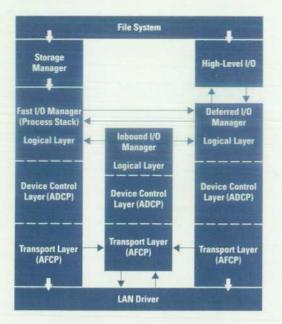

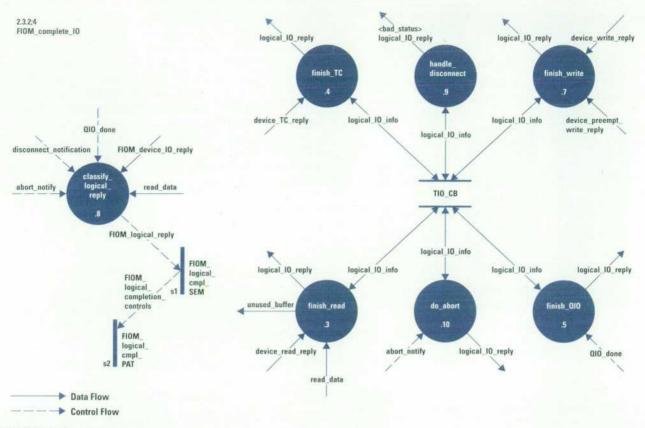

| 52 | Structured Analysis and Design in the Redesign of a Terminal and Serial Printer Driver,<br>by Catherine L. Kilcrease                       |

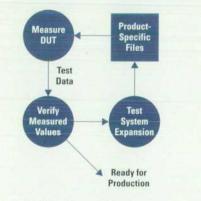

| 62 | Data-Driven Test Systems, by Adele S. Landis                                                                                               |

|    | Departments                                                                                                                                |

| 4  | In this Issue<br>Cover                                                                                                                     |

| -  |                                                                                                                                            |

- 5 What's Ahead

- 66 Authors

Editor, Richard P. Dolan • Associate Editor, Charles L. Leath • Publication Production Manager, Susan E. Wright • Illustration, Renée D. Pighini • Typography/Layout, Cindy Rubin

Advisory Board, Thomas Beecher, Open Systems Software Division, Chelmsford, Massachusettes • Steven Brittenham, Disk Memory Division, Boise, Idaho • William W. Brown, Integrated Circuit Business Division, Santa Clara, California • Frank J. Calvillo, Greeley Storage Division, Greeley, Colorado • Harry Chou, Microwave Technology Division, Santa Rosz, California • Derek T. Dang, System Support Division, Mountain View, California • Kajeh Dessi, Commercial Systems Division, Cupertino, California • Kavin G. Eveerl, Integrated Systems Division, Santa Clara, California • Barnhard Fischer, Böblingen Medical Division, Böblingen, Germany • Douglas Gennetten, Greeley, Hardcopy Division, Greeley, Colorado • Gary Gordon, HP Laboratories, Palo Alto, California • Matt J. Harline, Systems Technology Division, Roseville, California • Barnhard Fischer, Böblingen Medical Division, Santa Rosz, California • Barala H. Kanarek, Inkjet Components Division, Crevallis, Dregon • Thomas F. Kraemer, Colorado Springs Division, Colorado • Buby B. Lee, Networked Systems Grup, Cupertino, California • Altred Maute, Waldbronn Analytical Division, Waldbronn, Germany • Dona L. Miller, Worldwide Customer Support Division, Mountain View, California • Michael P. Moore, VXI Systems Division, Loveland, Colorado • Shelley I. Moore, San Diego Printer Division, Santa Peripheraks Division, Singapore • Ken Poulton, HP Laboratories, Palo Alto, California • Guinet Reisense Division, Bornetally, California • Han Tian Phua, Asia Peripheraks Division, Mountain View, California • Division, Loveland, Colorado • Garty Orsolini, Joreland, Colorado • Shelley I. Moore, San Diego Printer Division, Santa Peripheraks Division, Singapore • Ken Poulton, HP Laboratories, Palo Alto, California • Guinet Riebesell, Böblingen Instruments Division, Bablingen, Germany • Matc Sabatella, Software Engineenng Systems Division, Fort Collins, Colorado • Otto and • Guinets, Integrated Circuit Business Division, Covallis, Dregon • Philip Stenton, HP Laboratories Bristo, Bristol, England •

@Hewlett-Packard Company 1994 Printed in U.S.A.

The Hewlett-Packard Journal is printed on recycled paper.

August 1994 Volume 45 . Number 4

#### In this Issue

At first glance the HP 48GX advanced scientific graphing calculator looks exactly like its predecessor the HP 48SX scientific expandable calculator. With the exception of a few changes in the key labels both calculators are physically the same. The big difference is in functionality. In addition to having all the functionality of the HP 48SX, the HP 48GX has more advanced problem solving features, such as polynomial root finding and Fourier transforms, expanded memory capability (up to 4.75M bytes of address space), and seven new plot types including 3D and animation. A major attribute of the HP 48GX is a much improved user interface. As described in the article on page 6, one of the main design objectives for the HP 48GX was to make the calculator easy to use for both novice

and experienced users. To help accomplish this and other objectives a team of six mathematics professors were recruited to help design the HP 48GX. For the user interface, dialog boxes much like those found in an Apple Macintosh or Microsoft<sup>®</sup> Windows PC are used. Users are presented with input forms to fill in for a particular task and are given application-specific keys for acting on the data filled in. To handle all the new features and an expanded address space, an improved (in speed, cost, and manufacturability) CPU was built and a new memory controller configuration was developed for the HP 48GX. The article describes the hardware design for the HP 48GX and the differences in memory controller configurations between the HP 48SX and the HP 48GX.

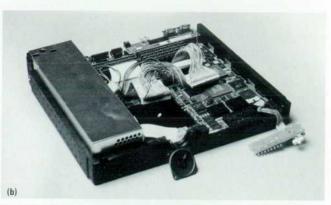

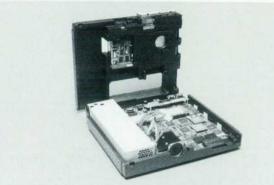

Environmentally friendly, easy to manufacture (i.e., manufacturability), low parts count, and low cost are some of the phrases we hear used today to characterize what an ideal product design should be. The article on page 23 describes a chassis and electronic component housing concept developed by the Mechanical Technology Center at HP's Böblingen Manufacturing Operation for trying to provide the "ideal" product design. This packaging concept, called HP-PAC, replaces the traditional metal chassis with expanded polypropylene foam for housing electronic parts. The article describes how this concept was used on a typical HP workstation chassis, resulting in a reduction in mechanical parts, screw joints, assembly time, disassembly time, transport packaging, and housing development costs. In addition, all this was achieved with an environmentally friendly, recyclable material.

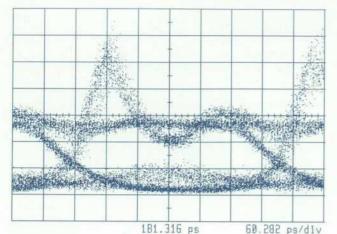

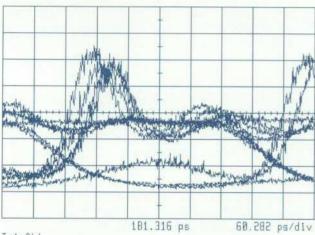

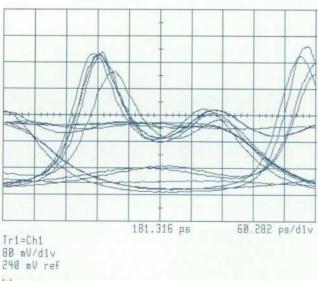

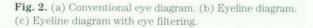

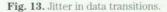

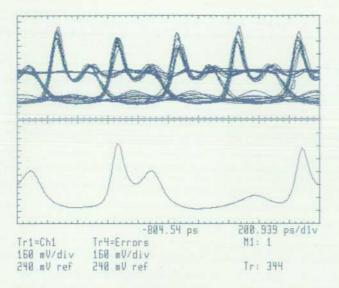

The quality of any transmission system is based on how well it can transmit error-free information from one location to another. In a digital transmission system, the primary metric used to measure this quality is the bit error ratio, or BER. The BER is defined as the number of bits received in error divided by the number of bits transmitted. Although the BER value does convey some important information, it is only a pass/fail parameter and it does not tell the complete story about the quality of a digital transmitter. Therefore, a typical BER test system includes an oscilloscope or an eve diagram analyzer for doing time-domain measurements on the transmitted waveform. An eye diagram is a waveform that has an opening like an eye, and in general the more open the eye the greater the likelihood that the receiver system will be able to distinguish a logical 1 from a logical 0. The HP 71501A eye diagram analyzer described in the article on page 29 provides the means to characterize high-speed digital transmitters using eve diagram analysis. The instrument constructs both conventional eye diagrams and special eyeline diagrams to perform extinction ratio (ratio of maximum to minimum optical transmission in dB) and mask tests (tests used to measure the size and shape of the eye). The article describes how the instrument uses a technique called harmonic repetitive sampling to construct eye diagrams similar to those produced by digital sampling oscilloscopes. A modified version of the sampling technique is used to construct eveline diagrams. With the modified sampling technique the samples or dots can be connected so that a whole trace or a portion of a bit sequence can be displayed at one time, enabling the eveline diagram to provide more information than the conventional eve diagram.

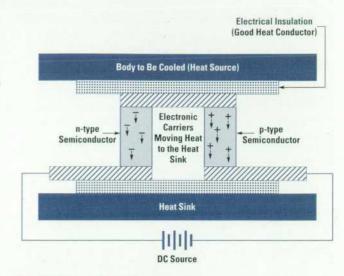

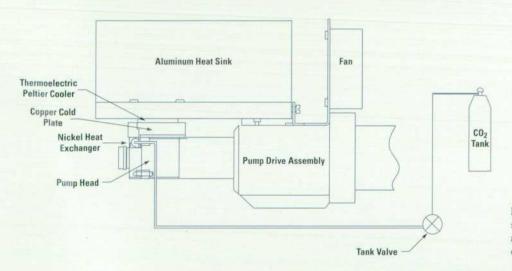

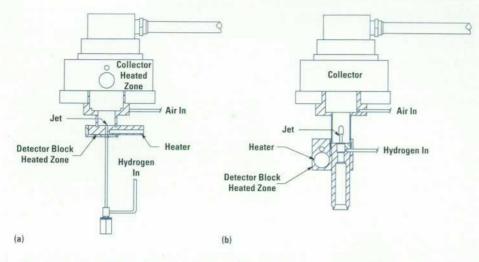

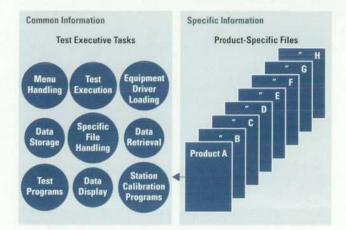

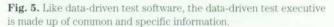

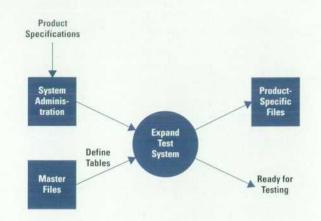

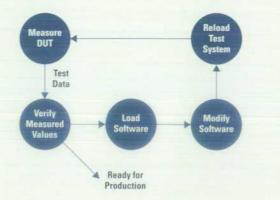

Four of the papers in this issue are from the 1993 HP Technical Women's Conference. In supercritical fluid chromatography temperature control is very important. Cooling is critical on the fluid supply end of the system and heating is critical on the separation end. The paper on page 38 describes the challenges engineers at HP's Analytical Product Group faced in modifying components from existing HP GC and LC products to meet the thermal requirements of the HP G1205A supercritical fluid chromatograph. Increasingly, test software development consumes the majority of the time spent developing manufacturing resources for electrical test processes required for new instrument products. In the paper on page 62 the author describes a test system that exploits the commonality among instruments to reduce test software development time.

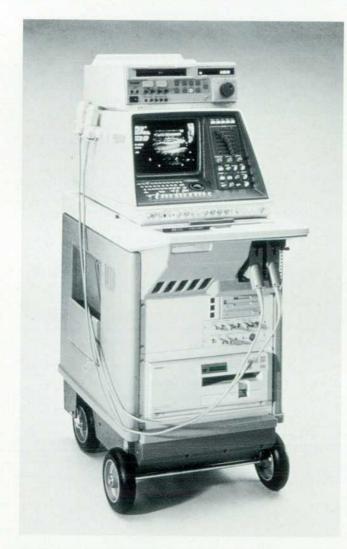

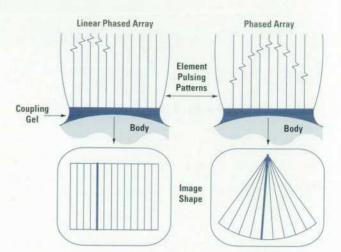

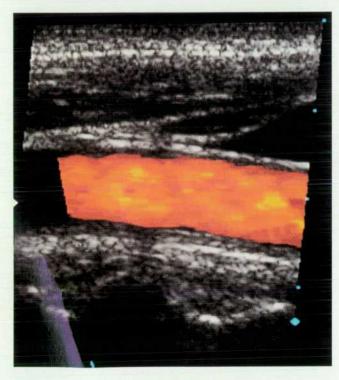

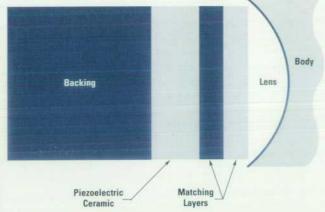

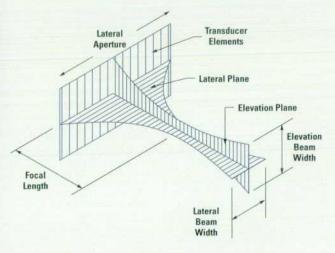

Improving the near-field image guality of the HP 21258A linear phased-array transducer, which is used for vascular ultrasonic imaging, was the main goal for the engineers at HP's Imaging Systems Division. The paper on page 43 provides a basic overview of ultrasound imaging (comparing sector phased-array and linear phased-array transducers) and then describes how customer feedback helped to guide the design of two new vascular transducers. > Most of the software literature that discusses structured analysis and structured design techniques focuses on applying the techniques to the development of new software systems. The paper on page 52 describes the application of structured analysis and design to the redesign of an existing system. The article describes how the techniques were used to lay out the existing system so that areas for redesign and improvement could be easily identified. The paper also includes examples of redesigned modules and recommendations for software projects considering using structured analysis and design techniques for a redesign effort.

> C.L. Leath Associate Editor

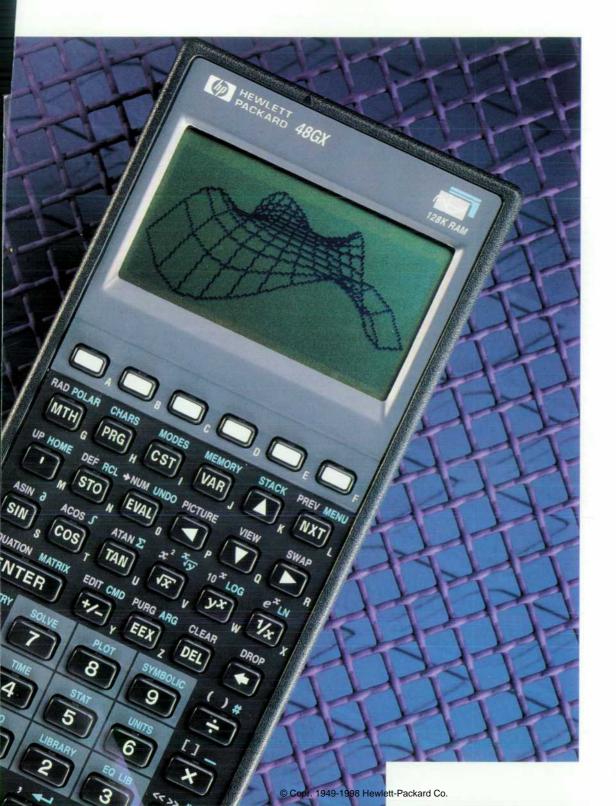

#### Cover

The HP 48GX advanced scientific graphing calculator displays a wireframe plot of the surface  $z = x^3y - xy^3$ .

#### What's Ahead

In the October issue, seven articles will describe the design and development of the first two VXIbus modules for the HP HD2000 data acquisition system: the HP E1413A 64-channel scanning analog-to-digital converter and the HP E1414A pressure scanning analog-to-digital converter. Four articles will discuss various aspects of the design and applications of the HP 9493A mixed-signal LSI test system. There will also be design articles on the HP 4291A high-frequency impedance analyzer, the HP 15800A virtual remote software, and the FDDI Ring Manager application for the HP Network Advisor protocol analyzer. Other articles will discuss frame relay conformance testing and an electrical overstress test system.

Microsoft is a U.S. registered trademark of Microsoft Corporation. Windows is a U.S. trademark of Microsoft Corporation.

## **An Advanced Scientific Graphing** Calculator

The HP 48G/GX combines an easy-to-learn graphical user interface with advanced mathematics and engineering functionality, expanded memory capability, and seven new plot types.

#### by Diana K. Byrne, Charles M. Patton, David Arnett, Ted W. Beers, and Paul J. McClellan

The HP 48G/GX, Fig. 1, is a state-of-the-art graphing calculator that combines an easy-to-learn graphical user interface with advanced mathematics and engineering functionality. It • Differential equation solvers is a continuation of the HP 28S1 and HP 48S/SX2 series of calculators, which are designed for high power, extendability, and customizability.

The HP 48G/GX includes improvements to address the needs of both novice and advanced users of scientific and graphing calculators. For the new user or the user who does not use certain functionality very often, the calculator has a dialog-box-style, fill-in-the-blanks user interface.

Fig. 1. HP 48GX scientific graphing calculator.

For the user who needs to do advanced problem solving, the calculator offers the following features:

- Polynomial root finder

- · Financial problem solver

- Library of engineering equations and constants

- Fourier transforms

- Matrix manipulations

- Linear algebra operations.

For the user who needs more memory and extendability, the GX version has 128K bytes of built-in RAM, compared to 32K bytes in the S and G versions. The only other difference between the G and the GX is the two memory card slots in the HP 48GX. The second memory card slot accepts up to 4M bytes of RAM or ROM.

The graphing capability has been expanded with the addition of seven new plot types, for a total of fifteen. The HP 48S/SX has function, polar, parametric, conic, truth, histogram, bar, and scatter plots and the HP 48G/GX has these plus differential equation, slope field, wireframe, parametric surface, grid map, pseudocontour, and y-slice cross-section plots.

The HP 48S/SX functionality has been retained in the HP 48G/GX. The new calculator has twice the ROM and retains much of the original code. The HP 48S/SX and HP 48G/GX both have the following features:<sup>2</sup>

- Unit management

- MatrixWriter

- EquationWriter

- HP Solve numeric solver

- RPN-style stack calculation

- Symbolic mathematics

- Time and alarms

- Statistics operations

- · Variables and directories for data storage

- · User-definable keyboard and custom menus

- RPL programming language

- Two-way infrared communications link

- RS-232 serial cable connector.

#### **Education Trends**

The creation of the HP 48G/GX can be traced to the American Mathematical Society (AMS) meeting in January 1992. We had been closely following the trend of using technology in the mathematics classroom because our software team

includes former mathematics educators and a calculus textbook author, and because we visit mathematics, engineering, and education conferences and talk to educators both to promote existing products and to find out what teachers and students would like to see in future products.

We had watched the interest in graphing calculators grow steadily each year, and had been involved in workshops for teachers using technology in the classroom through an HP grants program. Although the HP 48S/SX was becoming a standard for engineering students and professional engineers, it was just the first step in meeting the needs of the education community, and we continued to hear that it was too difficult to use and too expensive for classroom use. By January 1992, when we talked to educators attending the AMS meeting about their needs and about the calculators that they were considering for use in the classroom, it became obvious that we needed to have a new product for the education market no later than the 1993 back-to-school period. This resulted in the formation of an education advisory committee, a group of six mathematics professors who would help us design the calculator to fit the needs of the education community, and then give us feedback on our implementation.

#### **Design Objectives**

Our number one objective for the new calculator was ease of learning. The users of the HP 48S/SX told us that they appreciated its power, but its complexity made it difficult for both novice users and experienced users. The novices tended to be intimidated by the extensive owner's manual and the difficulty of mastering so many new operations, while the experienced users had a hard time remembering how to use some operations that they did not use frequently.

Creating a state-of-the art graphing calculator was our second objective. We needed to add some graphing capabilities, such as tracing along a graph and shading between graphs, just to maintain parity with other graphing calculators, but we also wanted to go far beyond the competition with features such as 3D graphing and animation.

Our third objective was to enhance the high-end mathematics capability of the HP 48S/SX with the addition of features such as differential equation solving, polynomial root finding, more matrix operations, and Fourier transforms, thereby strengthening our position as the most powerful technical calculator in the world.

By offering two models, the HP 48G and the HP 48GX, we intended to please customers at both ends of the education spectrum. The HP 48G has a list price that represents a substantial decrease from the list price of the HP 48SX or HP 48S. This makes the HP 48G competitive with other graphing calculators and makes it appealing even at the high school level. The HP 48GX has more appeal for college students, with four times as much built-in memory and two plug-in card ports that are expandable to 4M bytes of memory.

#### **Operating System**

A calculator or computer operating system is primarily a set of conventions for memory organization, data structures, and resource allocation together with a set of software tools to aid in performing operations in accordance with those conventions. In contrast, an application is software built using the resources and conventions of the operating system. As new hardware resources become necessary and available, the operating system must grow to manage those resources effectively and as transparently as possible to the applications built on the system.

The operating system (and system programming language) in the HP 48G/GX is the RPL operating system, first used in the HP 18C and HP 28C and subsequently in a number of other machines including the HP 28S, HP 48S/SX, and now, with extensions, in the HP 48G/GX.

#### HP 48G/GX Fundamentals

The key concept underlying the operation of the calculator is the idea of objects on the stack. A stack is a data structure that is similar to a stack of cafeteria trays. The clean trays are added to the top of the stack, and as trays are needed, they are removed from the top of the stack. This type of last in, first out ordering characterizes the HP 48G/GX stack. All operations take their arguments (if any) from the stack and return their results (if any) to the stack.

There is only one data stack in the HP 48G/GX. This resource is shared by the user and the system RPL programmer, who must take great care to make sure that any objects that belong to the user are preserved through the operation of system RPL programs. For example, the user may have a few numbers sitting on the stack, then decide to plot the graph of a function. The system RPL program that runs when the DRAW key is pressed does many operations that require the use of the stack, such as recalling the plotting parameters, checking that they are valid, calculating the range over which to plot, evaluating the user's function, and converting the function values to pixel coordinates. After the graph is complete (or if the drawing of the graph is interrupted by the user), when the user sees the stack again, the same numbers that were there to begin with should not have been disturbed.

Instead of trays, users may collect various types of numeric, symbolic, and graphic objects on the HP 48G/GX stack. The types of objects available in the HP 48G/GX include real and complex numbers, real and complex arrays, binary integers, names, characters, strings, tagged objets, algebraic objects, unit objects, and graphic objects. There are also backup objects, library objects, directories, programs, and lists. (HP 48 object types are discussed in more detail in reference 2.)

In a key-per-function calculator, there is a single key that the user needs to press to get the machine to perform any operation, such as cosine. The HP 48G/GX has many more operations than the 49 keys on the keyboard, so there needs to be a way to access all the functionality without assigning one operation to each key on the keyboard. This is accomplished through the use of menus and softkeys. The top row of keys on the keyboard do not have anything printed on them because they correspond to menu labels that appear along the bottom of the screen. These keys are called softkeys, and their meaning changes whenever the corresponding labels on the screen are changed by the software.

#### HP 48S/SX Memory Controller Configurations

We will now discuss the memory controller configurations used in the HP 48S/SX and how these are used in implementing the various types of expanded address modes developed for these products. The next section outlines the differences

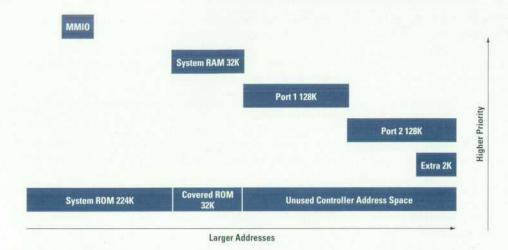

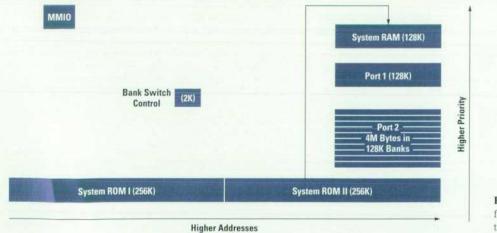

Fig. 2. Standard memory controller configuration for the HP 48S/SX calculator. Memory sizes are in bytes.

in configuration between the HP 48S/SX and the HP 48G/GX and discusses how these differences are used to extend and refine the expanded address technology to provide access to a total of 4.75M bytes of code and data as transparently as possible.

The CPU bus architecture first developed for the HP 71 and used in all HP calculators since that time has several useful features. One of the nicest is its address configuration capabilities. All chips attached to the bus are required to be able to change, on command of the bus, the range of addresses that evoke a response from the chips. Such a system eliminates, once and for all, the inconvenience and headache of configuring jumper switches on cards designed to plug into the machine. For a consumer product like a calculator this is not only a nicety, it is a necessity.

In the early days of the architecture (HP 71 to HP 28C), the CPU bus lines were actually routed around the circuit board and any RAM, ROM, or memory mapped I/O that was attached to the bus had to be custom-made with the bus interface attached. This had the advantage of allowing an arbitrary number of parts to be added to the system with assurance that the system would be capable of handling all of them in one way or another. It had the grave disadvantage of putting a price premium on such essential items as ROM and RAM.

In the second-generation CPU chip, a fixed number of memory controllers were included onboard the CPU. The CPU bus was then, for all practical purposes, completely hidden within the CPU itself. The combination of external standard RAM or ROM together with one of the internal memory controllers was then equivalent (so far as the CPU bus is concerned) to a standard bus device.

In the standard device implementations, the size of the device (that is, the address space occupied by the device) is designed into the device. In the second-generation chip, the size of the controllers was mask programmed at the time of manufacture since we knew exactly what size each controlled device would be.

With the advent of plug-ins for the HP 48S/SX, the configuration capabilities of the memory controllers had to be expanded to include varying the apparent size of the memory controller to conform with the device being plugged in. This is one of the many advanced features in the third-generation, HP 48S/SX implementation of the architecture. This resizing feature, in addition to allowing plug-ins of various sizes, also presented the opportunity to explore expanded address modes, which we have come to call the "covered" technology, for reasons that will be apparent shortly.

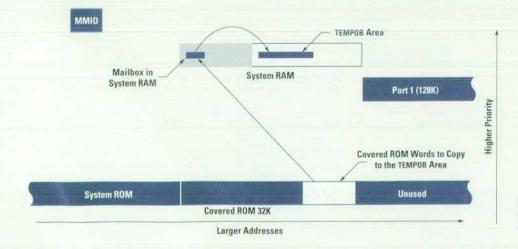

The third-generation CPU chip has six memory controllers. In the HP 48SX, these are allocated to memory mapped I/O, system RAM, port 1, port 2, and system ROM, and there is one extra controller. Their configuration in the usual state is shown in Fig. 2. The memory controllers are shown with their sizes and locations in the address space (00000h to FFFFFh). They are also pictured as having a vertical location in "priority space." In the CPU bus definition the devices are chained, with the result that devices closest to the CPU on

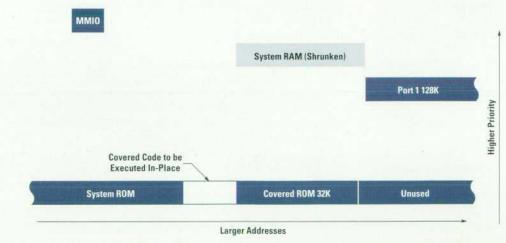

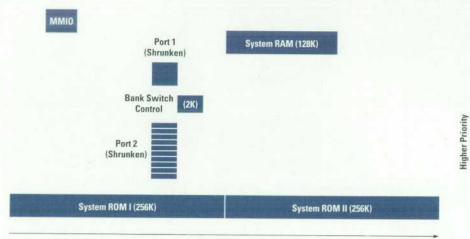

Fig. 3. Execute-in-place configuration for HP 48S/SX covered code.

8 August 1994 Hewlett-Packard Journal

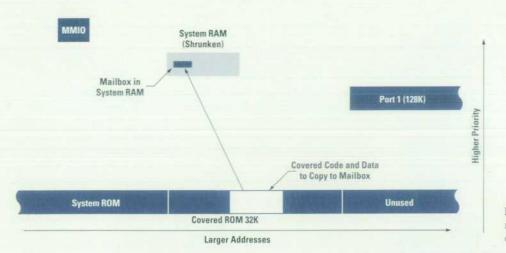

Fig. 4. Copy-to-mailbox configuration for HP 48S/SX covered data.

the chain have the first opportunity to respond to bus requests. In consequence, if two devices are configured with overlapping address ranges, the one closer to the CPU on the chain effectively hides the more distant one. In Figs. 2 to 12, higher priority can be interpreted as "closer to the CPU" or "hides those below."

As shown in Fig. 2, the memory controller for system RAM hides the section of ROM shown as covered. This is the reason for the name "covered" technology.

Fig. 3 shows more detail of the covered ROM and the first way in which it is used. In one section of the covered ROM there is assembly language code (mostly math routines) that requires no RAM resources outside the CPU for execution. This code is executed in-place in the covered ROM by shrinking and/or moving the memory controller for system RAM so that the relevant section of code is temporarily uncovered. When the routine finishes execution, system RAM is returned to its normal configuration.

A second set of routines, all of which only need access to a fixed set of locations within system RAM, can execute with system RAM in any one of 16 locations, as long as they themselves are not currently covered by system RAM.

Fig. 4 shows a second way in which the covered ROM is used. In this case, code and data (mostly data) are copied from covered ROM to a mailbox at a fixed location in system RAM. After the copy is completed, system RAM is returned to its normal configuration and the code and data are available to the rest of the system. Coders using this data must remain aware that it is volatile and can be destroyed by another fetch of data from covered ROM. In this sense, this method is not transparent.

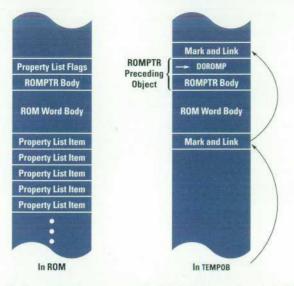

Another way in which covered ROM is used is shown in Fig. 5. It is as transparent as the execute-in-place method but entails fewer restrictions on the code and data that can be included. In the HP 48SX code, this system is usually tied to the execution of ROMPTRs. Recall that ROMPTRs are RPL objects that substitute for hard addresses of objects whose precise location is not known in advance (and in fact might not even be present.) They are midway between hard addresses that only change at compile/link time and identifiers whose corresponding objects may move between subsequent calls at run time.

If, during the conversion of a ROMPTR to an address, it is determined that the corresponding object lives in covered ROM, the object is copied from covered ROM, through the mailbox, to the TEMP0B (temporary object) area. The address of its new location in the TEMP0B area is then returned. Fig. 6 shows a comparison of a named ROM word (keyword or command) as it would exist in covered ROM and as copied to the TEMP0B area. Although we'll refer back to Fig. 6 later, for now notice that in addition to the object itself, an additional piece is added to the image in the TEMP0B area. This piece is a ROMPTR preceding the object itself. This allows

Fig. 5. Copy-to-TEMPOB configuration for HP 48S/SX covered ROM words.

**Fig. 6.** Comparing the structure of a ROM word as resident in ROM and when copied to TEMPOB using covered technology.

the routine converting the ROMPTR to an address to check whether the object in question is a copy of one residing elsewhere. This method of covered ROM access, which we call "covered ROM word access," will be especially relevant to our discussion of the HP 48G/GX.

Preexisting design elements of the RPL system contributed greatly to the practicality and transparency of covered ROM word access, including:

- Encapsulation of code and data into RPL objects that are of determinable size

- Indifference of RPL object execution to object location in RAM or ROM

- Equivalence of direct and indirect execution of RPL objects, which allows (noncircular) structures to be stored and used in the same format.

#### HP 48G/GX Memory Controller Configurations

The HP 48GX has a number of important features including:

- Up to 128K bytes of built-in system RAM

- One plug-in port electrically equivalent to the HP 48SX ports

- Access to 512K bytes of system ROM

- Access to 4M bytes of RAM or ROM at a second port using industry-standard parts.

These features required increasing the usable address space from 0.5M bytes to 4.75M bytes, an 850% increase over previous machines.

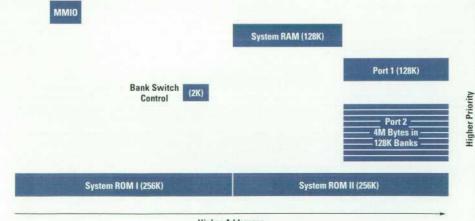

While the HP 48G/GX has CPU functionally equivalent to the third-generation CPU discussed above and thus has six memory controllers, these controllers are configured and used differently. Fig. 7 shows the standard HP 48GX configuration. The controller previously allocated to port 2 is now used as a bank switch control, and the extra controller is now allocated to port 2. Furthermore, there are now as many as 34 layers over the last 128K bytes of address space.

Eliminated in this configuration is the HP 48S/SX covered ROM. This means that all of the functionality included in the HP 48S/SX can be accessed more quickly. Two things that are visibly enhanced are plotting (since the math routines are not covered) and screen update (since the font bitmaps are not covered.) Since there are a great many more covered places to access, however, there are many more "temporary" configurations to keep track of while working with the covered data.

To simplify the system, we use only a single covered technique, namely, covered ROM word access, with appropriate modifications. Without this simplification, the number of access method and configuration combinations would be unmanageable. Moreover, this is the only feasible method of covered access to code written for the HP 48S/SX or not expressly written for the the new configuration.

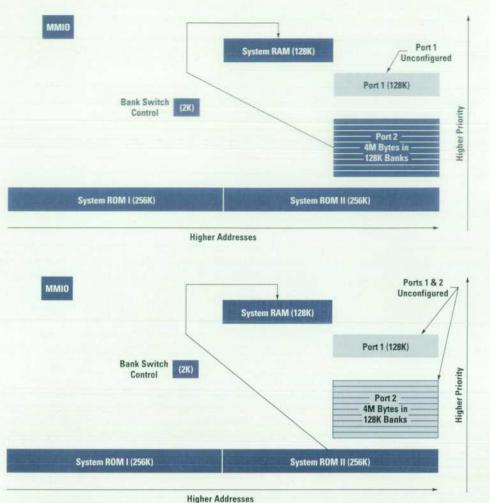

Fig. 8 shows the configuration while copying an object from a bank of port 2 to the TEMPOB area. Port 1 is unconfigured. In the unconfigured state, the controller responds to only a handful of bus commands and acts as if it weren't there for data access.

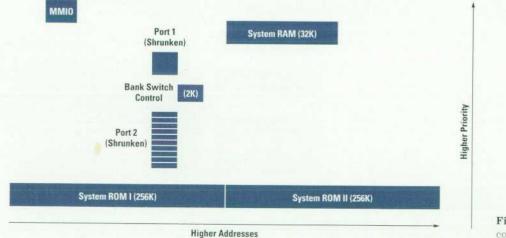

Fig. 9 shows the configuration while copying an object from the second half of the upper system ROM. In this case, both ports are unconfigured.

Fig. 10 shows the configuration while copying an object from the first half of the upper system ROM. Since a controller move or resize operation takes many more CPU resources than configure or unconfigure, it is often necessary to copy objects from this section, through a mailbox, and then into the TEMPOB area.

Higher Addresses

Fig. 7. HP 48GX standard memory controller configuration.

Fig. 8. HP 48GX configuration for copying an object from a bank of port 2 to TEMPOB.

**Fig. 9.** HP 48GX configuration for copying an object to TEMPOB from the upper half of system ROM.

Fig. 11 shows the configuration when it is determined that nothing is plugged in at all. In this case, the only covered access is to the first half of the upper system ROM. Again, it is likely to be necessary to copy this material through a mailbox. Otherwise, all the ROM words can be executed in-place.

Fig. 12 shows the standard HP 48G configuration, which is identical to Fig. 11 except for the smaller size of system RAM. While it is not strictly necessary to use this configuration, which matches one of the HP 48GX configurations, there are advantages. First, it allows maximal code sharing between the two machines. In fact, the code can be identical in this case. Second, it gains the advantage of faster access to the base functionality, providing a more responsive implementation.

#### **Hardware Design**

The heart of the HP 48G/GX is a fourth-generation CPU chip. This custom ASIC is built around the original HP 71 processor, and its development was key to the creation of the HP 48G/GX. This chip has four advantages over the thirdgeneration chip used in the HP 48S/SX. First, it is produced

Fig. 10. HP 48GX configuration for copying an object to TEMPOB through a mailbox.

**Higher Addresses**

Fig. 11. HP 48GX all-ports-empty configuration.

using a different CMOS process, allowing better stability with onboard voltage regulation circuitry. Second, these improved voltage characteristics and several low-level optimizations allow the new CPU to operate at twice the speed of its predecessor. This speed increase gives it a 4-MHz bus rate. Third, the new CPU is packaged in a 160-pin quad flatpack, improving the manufacturability of the HP 48G/GX. Fourth, with all these improvements, the final cost is lower, increasing the budget for other hardware improvements to the calculator.

The faster processing speed of the HP 48G/GX CPU gave the software team incentive to improve the user interface, implementing graphical routines that would not have been acceptable at the slower processing rate. This added functionality required an increase in data storage space, so we boosted the size of ROM and RAM. We also decided to add the facilities to bank-switch a data card plugged into card port two.

The HP 48G/GX circuitry, with its additional components, had to fit in the same physical space as in the HP 48SX. The product plan and schedule did not allow changes to production tooling or plastic parts except for those that were absolutely necessary. At times we felt like poets trying to write crossword puzzles. The HP 48SX circuit board design was optimized such that it did not leave us much free space. These space constraints affected many of the HP 48G/GX hardware design choices.

The RAM increased from 32K bytes in the HP 48SX to 128K bytes in the HP 48GX, while the HP 48G retained the original 32K-byte chip. This difference between the G and the GX offers two advantages. First, it provides more differentiation between the functions and cost of the G and the GX, increasing the product family's market appeal. Second, the difference in RAM size provides a way for the calculator to know whether it is a G or a GX. If the calculator scans the RAM and finds only 32K bytes, then there will never be a plug-in data card installed. With this information the covered memory options become much simpler. The RAM memory size becomes an internal product type identifier, and several software routines are optimized for faster performance on the HP 48G.

#### **ROM Changes**

The HP 48G and GX share a common ROM code set. They also share a common circuit board. While this simplifies documentation, manufacturing, and stock control, it also complicates some areas. The HP 48GX RAM chip is wider and longer than the chip used in the HP 48G: the 32K RAM is in a 28-pin small-outline package (SOP), and the 128K device is a 32-pin SOP. Both conform to the JEDEC pinout standard. A 128K device was chosen that has an extra chip select line at pin 30. This chip select is tied high, allowing pins 1 through 28 of the smaller RAM to overlay pins 3 through 30 of the larger device. The extra chip select of the HP 48GX RAM

Fig. 12. HP 48G standard configuration.

matches the  $\rm V_{dd}$  line of the HP 48G RAM chip, and all of the other lines are pinout-compatible.

The difference in physical package width also posed a problem. The foil patterns on the circuit board had to be modified to accept RAM chips with different lead spacings across the package. The immediate response was simply to stretch the oval-shaped patterns. However, this resulted in the foil extending well under the body of the 128K chip, a situation that could have led to solder bridging where the solder paste contacted the part body. This is avoided by using two different solder stencils on the manufacturing line. A paste of solder is laid on the blank circuit board before parts are loaded onto the board. A metal stencil defines the pattern of the solder paste, just as a silk screen controls the pattern of ink on a shirt. By using a different stencil pattern for the G and GX circuit boards, we control the original location of the solder paste and keep it out from under the 128K-byte RAM body. Once all the components are loaded onto the circuit board and the solder is heated to a molten state, a danger might again exist for the solder to flow under the part body. Fortunately, the nature of the mechanical contact between the RAM lead and the circuit board foil tends to cause the solder to pool or wick to the lead rather than spreading across the elongated foil pad.

The packaging of the ROM chip was also changed between the HP 48SX and the HP 48GX. The SX used a square 52-pin quad flatpack for its 256K bytes of program data. The code size of the HP 48GX is doubled to 512K bytes. Its package is a 32-pin SOP like the 128K-byte RAM chip. Their common package configuration allowed us to conserve space in the placement of the two chips and in the routing of signal wires between them.

Use of a standard SOP ROM chip also allowed us to use onetime programmable (OTP) ROMs in prototype calculators. An OTP uses the same semiconductor core as a UV-erasable EPROM. To get the semiconductor chip into an SOP, however, the manufacturer omits the familiar glass window in the chip, covering the device in opaque plastic. The resulting ROM is no longer erasable.

Typically, a product schedule requires months between code release and the start of production so that ROMs can be built with the software code built-in. The use of OTPs on this project cut the required time from months to days. For one prototype run, the time between code availability and product build was only a few hours.

The HP 48G/GX CPU multiplexes the highest address bit, A18, with an additional chip enable line, CE3. The original idea was to allow future expansion of the HP 48 family, either to use a larger ROM chip or to include an additional memory mapped device. By the time the HP 48G/GX design was complete, we had decided to do both. We doubled ROM to 2<sup>19</sup> bytes, and we added bank switching to card port 2. Two small HCMOS chips were added to the board to demultiplex these signals. The two chips are a quad NAND chip and a hex D flip-flop, similar to the standard TTL devices. The multiplexing is accomplished by simply toggling a control bit inside the HP 48G/GX CPU. To demultiplex the A18 and CE3 signals, we developed a protocol for mirroring the state of the internal bit to one of the external D flip-flops. The NAND

gates handle signal demultiplexing, and the remaining five flip-flops form a register for the card port 2 bank address.

#### Other Hardware Changes

The card ports of the HP 48SX were designed for Epson memory cards. Several unused lines were adapted to provide external video signals to drive an enlarged display for classroom use. On the HP 48GX, the video lines are replaced by five additional address lines. The system software allows the card in port 2 to be subdivided into 128K-byte sections, with each section treated as a virtual plug-in card. Five bank select address lines permit up to 32 virtual plugins in card port 2, yielding a maximum card size of 4M bytes in the plug-in port. With the ROM, RAM, and plug-in options, an HP 48GX can access 4,980,736 bytes of onboard data.

Since the inception of the HP 48 family of calculators, liquid crystal display technology has progressed significantly. The display in the HP 48G/GX provides improved visibility by improvements in pixel contrast. The display is thinner than before. This change in glass thickness reduces the parallax between the pixel within the display and its shadow on the rear face of the display. In the HP 48SX, the pixel contrast was lower and the shadow was not dark enough to cause problems, but in testing the new HP 48G/GX display under various light conditions, we found that shadow effects made the display hard to read. With the thinner glass now used, the pixel and its shadow appear as one image, and the shadow now enhances the appearance of the pixel.

Changes to plastic parts were not permitted, except where necessary. The back case of the HP 48G/GX required changes. The changes were all accomplished by making mold inserts. Where text on the mold needed changes or additions, the affected area of the mold was milled away. A piece of steel was placed into the hole to make a perfect fit, and the face of this new piece was etched or inscribed with the new textures and features. The new back case helps identify the differences between card ports 1 and 2, updates the copyright information, adds a mark indicating that the HP 48G/GX complies with Mexico's importation laws, and adds an area for a customized nameplate. The customized nameplate is a piece of metal with adhesive on one side. The customer's name can be engraved on the plate and attached to an inset area of the back case. This is the same nameplate used on HP's palmtop computer family.

The result of these changes is a computer platform that is more powerful than its predecessor, is well-suited to the enhanced user interface developed by the software team, is more versatile for both the user and the design engineer, and is less expensive to produce. It started as a processor upgrade and became a major product improvement.

#### **User Interface**

With ease of learning and ease of use the primary goals for the new HP 48G/GX calculator, the user interface and many built-in applications have been largely redesigned.

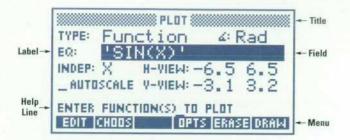

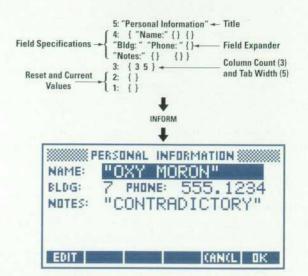

*Input forms* provide the common starting point for the new and rewritten applications in the HP 48G/GX. Looking

Fig. 13. A typical input form.

much like dialog boxes in an Apple Macintosh or Microsoft<sup>®</sup> Windows PC, input forms provide a fill-in-the-blanks guide to the input needed for a task, plus application-specific menu keys for acting on that input.

For selecting an application in a particular topic and for picking an input from among several choices we developed *choose boxes*, a type of pop-up menu that suggests alternatives and narrows the input focus.

We designed *message boxes* to make feedback to the user more manageable within our increasingly crowded display space. Message boxes appear on top of whatever the user is working on and provide more flexibility for formatted messages and icons than the two-line, fixed-location error messages they replace. They also preserve the context that can otherwise be lost when something surprising happens within an application.

#### **Input Forms**

An input form provides both a means to enter data pertinent to an application and operations that permit the user to direct actions.

Visually, an input form consists of (see Fig. 13):

- A title suggesting the form's purpose

- One or more fields, typically with explanatory labels, which are used to gather and display user input

- A help line that details the input expected in the selected field

- Menu keys that provide more options for working within or exiting the input form.

Each input form field can be one of four types. Most input forms, such as the Set Alarm and I/O Transfer input forms, contain several or all types of fields. *Text fields* are used to enter arbitrary HP 48G/GX objects like real numbers and matrices; the object types allowed are specific to each text field. In Fig. 14, a text field is used to enter an alarm message in the Set Alarm input form.

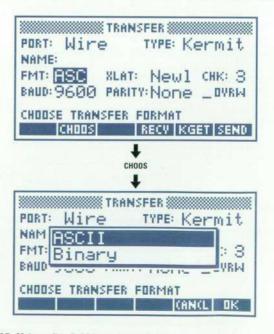

When a single choice among several is required, *list fields* are used to eliminate invalid input and to help focus user actions. To select an entry in a list field, a choose box is displayed. In Fig. 15, a list field is used to specify the transfer format in the I/O Transfer input form.

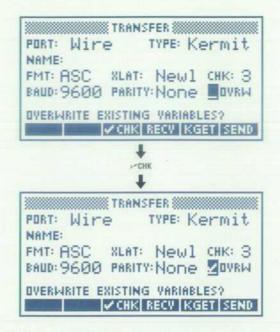

Sometimes only a simple yes-no, do-or-don't type of choice is needed. For this we use *check fields*. Fig. 16 shows how the overwrite (OVWR) field is used to specify whether or not an existing variable should be overwritten.

Finally, when arbitrary input is possible but logical choices are also available, *combined text/list fields* are employed. In

|                  | SET SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ALARM  |       |             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------------|

| MESSAGE          | LUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ICH AT | ' MO' | S"          |

| TIME:            | 12:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00:00  | PM    |             |

| DATE:            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6794   |       |             |

| REPEAT:          | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |       |             |

| ENTER AL         | ARM MI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ESSAGE |       |             |

| EDIT             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | (ANCL | 0K          |

|                  | 11 N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EDIT   |       |             |

|                  | CET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ALARM  |       |             |

| MESSAGE:         | and the second se | ICH AT | MO '  | <b>C</b> II |

| TIME:            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10:00  | PM    | 0           |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |       |             |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | FII   |             |

| DATE:            | 8/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6794   | E11   |             |

| DATE:<br>Repeat: | 872<br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26794  | гн    |             |

| DATE:            | 872<br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6794   | ги    |             |

Fig. 14. Using a text field in an input form.

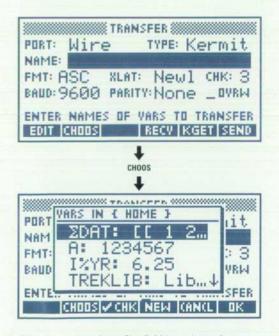

the Transfer input form, the Name field is a combined field that permits new names to be entered or the names of existing HP 48G/GX variables or PC files to be selected (see Fig. 17).

As the figures illustrate, each of the three base field types has associated with it a dedicated menu key that triggers the unique feature of that field type. This feature is an important part of how we maintained a calculator key-per-functionstyle interface within the constraints of a small display and with no pointing device. In other graphical user interfaces, visual elements such as list arrows are activated by mouse clicks to elicit different behaviors from fields. In the HP 48G/GX, the user's finger acts as the pointing device, triggering the desired behavior by pressing the appropriate action button for each field. Consistent location of the three types

Fig. 15. Using a list field in an input form.

Fig. 16. Using a check field in an input form.

of action buttons helps the user navigate an input form confidently.

Some input form menu keys perform application-specific operations—for example, DRAW in Plotting. In the second row of the input form menu are more advanced input form operations for resetting a field or the entire form, displaying the object types allowed in a field, and temporarily accessing the user stack to calculate or modify a field value.

#### **Choose Boxes**

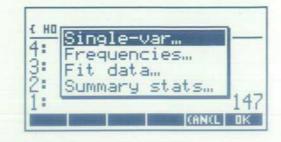

Choose boxes are used to make a choice in an input form list field. They are also used in most subject areas to choose a specific application from among several. Fig. 18 shows the choose box that is displayed when the STAT key is pressed to perform statistical calculations.

Fig. 17. Using a combined text/list field in an input form.

Fig. 18. A typical choose box.

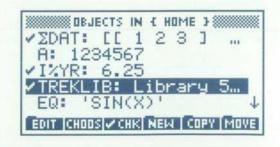

When circumstances require, choose boxes can include any or all of several advanced features. The Memory Browser application, for example, is actually a maximum-size choose box embellished with a title, multichoice capability, and a custom menu (see Fig. 19).

#### Message Boxes

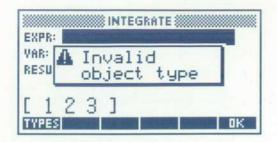

Message boxes are used primarily for reporting errors that require attention before proceeding. For example, if the user attempts to enter a vector in the EXPR field of the Integrate input form, a message box appears to inform the user of the problem (see Fig. 20).

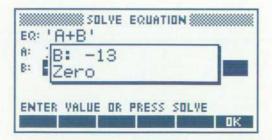

Some applications also use message boxes to give additional information. For example, in the Solve Equation input form, the user can press INFO any time after a solution has been found to review the solution and determine how it was calculated (see Fig. 21).

#### **Input Form Implementation**

For the HP 48S/SX, we developed an RPL tool called the parameterized outer loop<sup>3</sup> to speed development of new interfaces such as the MatrixWriter by automating routine key and error handling and display management. The input forms in the new HP 48G/GX embrace this concept—in fact, the input forms engine is a parameterized outer loop application—and take it one step farther to automate routine matters of application input entry and selection of options. The input forms engine brings a uniform interface to all new HP 48G/GX applications.

While narrowly focusing the task of application development by managing command input tasks, the input forms engine also leaves much room for the customization that helps optimize the HP 48G/GX for ease of use. Since an important measure of our progress towards our goals for the calculator was to be feedback from typical users throughout the development cycle, we designed the input forms engine from the ground up to be highly customizable. This was accomplished in a programmer-friendly manner by including

Fig. 19. The Memory Browser: a complex choose box.

Fig. 20. A typical message box.

over fifty hooks into the input forms engine's responses to external and internal *events*. *External events* are triggered by users and include low-level events such as key presses and high-level events such as completion of a field entry. *Internal events* are usually activated by external events, such as formatting a completed field entry for proper display. A single external event can trigger a half dozen or more internal events, all of which are customizable.

Input form applications can customize any or all form-level events such as title display or field events such as displaying a help line. Each field has a *field procedure* associated with it, and the entire form has a *form procedure* associated with it. Whenever an event occurs, the appropriate field or form procedure is called with an identifying event number and perhaps additional information. If the procedure does not customize the event, it returns FALSE to the input forms engine. If it does customize the event, the procedure performs the custom behavior and returns TRUE. In this manner, every event first queries the proper form or field procedure to determine if custom behavior is needed, then handles the event normally only if it isn't customized. If a form or field has no custom behavior, it specifies a default procedure that quickly responds FALSE to all event queries.

The reason for a form procedure and multiple field procedures is to spread the burden of customization throughout the form. Since each field procedure only checks for the events that pertain to it, and since the form procedure only checks for form-level events, no single event processing is slowed by a highly customized form that would otherwise have to compare the event number against a lengthy list of event and field combinations.

For the HP 48G/GX project we needed another layer of regularity not enforced by the input forms engine. Because we sought and reacted to usability feedback almost until the code was released to production, the user interface details for each subject area were subject to constant change. It was imperative, therefore, that we maintain a strict and formal

Fig. 21. The Solve Equation INFO message box.

division between unchanging and well-understood tasks such as getting and saving problem domain information and calculating results—and the user interface details that were changing regularly. We developed a set of conventions that were embodied in what we called *translation files*. We used naming rules and constrained responsibilities to greatly mitigate the effects of user interface changes on the underlying problem-solving functionality. For example, one RPL word in the plotting translation file has the simple task of reading the current horizontal plot range from calculator memory. Since the word has no presumptions about how and when it will be called, references to it could be (and often were) changed around as the fields populating the plotting input form were worked out.

#### **Choose Box Implementation**

The choose box engine is very much like the input forms engine. For customization, the programmer can supply a *choose procedure* that responds to 26 messages.

A feature of choose boxes that simplifies their use is the option—heavily used by the built-in applications—of items that encapsulate both display and evaluation data. For example, when an angle measure—degrees, radians, or grads—is to be chosen in certain input forms, the choose box engine displays plain descriptions but returns an RPL program that sets the selected angle measure. This circumvents the need for branching according to the returned object and simplifies the extension of choices.

#### **Results: Benefits and Costs**

Initial feedback from the educational advisory committee and user reviews suggests that the use of input forms and other graphical user interface elements has greatly improved the ease of use of the HP 48G/GX over the HP 48S/SX. However, the path we took to this accomplishment was more challenging than we planned.

Event customization, originally conceived as a means to extend the functionality of input forms in unforeseen ways, turned out to be a key component of our ability to prototype new user interface ideas rapidly. As their name may imply, the original intent of input forms was very modest compared to the role they now play. We designed input forms to be the standard means by which applications gather data for a task. One or more input forms would be displayed as necessary within the context of another, undefined, application context. This original concept is applied successfully throughout the calculator. For example, in the Memory Browser, when NEW is pressed to create a new variable, an input form is used to get the information required (see Fig. 22). In this context, the user can do only three things in the input form: enter data, cancel the form, or accept (OK) the form. This simple but effective behavior was the model used for the original input form design.

As the project developed, however, it became apparent that an input form could serve not only as a information gatherer but also as an action director. Input forms thus graduated from simple dialog boxes to full-fledged application environments.

| NEW VARIA        | BLE      |

|------------------|----------|

| NAME:            |          |

| _ DIRECTORY      |          |

|                  |          |

| ENTER NEW DBJECT |          |

| EDIT CHODS       | (AN(L DK |

Fig. 22. Memory Browser NEW input form.

Interestingly, no major changes to the input forms engine were necessary or even desirable to support their new role. Instead, the essence of input form functionality remained always data management, and the events customization was applied selectively where needed to enhance application forms.

In a similar manner, the event-driven choose box engine was eventually pressed into service as a powerful base for liststyle applications like the Memory Browser.

The combination of lean, focused, standard feature sets for input forms and choose boxes and high customizability proved invaluable during the calculator design refinement. Throughout the middle portion of the project, when the basics had been settled but many user interface details were still unclear, we were able to prototype new ideas quickly and realistically by customizing event responses.

Translation files were another development effort that helped us keep the design and implementation moving forward. However, we learned over time that their overhead caused some duplication of code and inefficiency to creep into the interface between the input forms and the calculator mainframe. We addressed this issue where possible by making simple and safe code substitutions while leaving the interface concepts intact to enable high-confidence code defect fixes late in the project. In effect, we made a choice between maintainability and high performance that still remains a controversial topic among the HP 48G/GX developers.

#### **3D Plotting**

The functionality described in this section is a suite of 3D graphing and viewing utilities for the HP 48G/GX. We had several requirements to consider in creating these routines. Our aims were that they be psychologically effective and require only a small amount of code.

In exploring visualization techniques on a variety of machines we found that increasing "realism" (ray-traced, Phong-shaded, hidden-line, etc.) in the graphical presentation of functions of two variables did not necessarily correlate with increasing ease of comprehension. The HP 48G/GX routines represent the results of some of these experiments (including time-to-completion as an important factor).

All of the 3D plotting routines are intended as seamless extensions of the other built-in plotting utilities. In particular, they share the same standard user interface and are selected as alternative plot types. The 3D plotting routines are SLOPE-FIELD, WIREFRAME, YSLICE, PCONTOUR, GRIDMAP, and PARSURFACE. Like the other plotting routines, all the 3D plotting routines assume that the function of interest is stored in EQ.<sup>3</sup> Further, they assume, by default, that the function is represented as an expression in the variables X and Y—for example,  $u, v \rightarrow sin(u+v)$  is represented as SIN(X+Y) in EQ. The use of other variable names is provided for by input form options or by the INDEP and DEPEND keywords.

While this section is titled "3D Plotting," a better name would be "visualization techniques for functions of two variables." This would cover the perspective view of the graph of a scalar function of two variables (WIREFRAME), the slicing view of a scalar function of two variables (YSLICE), the contour-map view of a scalar function of two variables (PCONTOUR), the slope interpretation of a scalar function of two variables (SLOPEFIELD), the mapping grid visualization of a two-vectorvalued function of two variables (GRIDMAP), and the image graph of a three-vector-valued function of two variables (PARSURFACE).

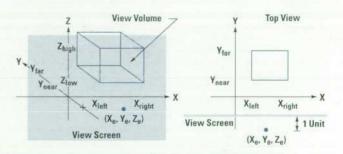

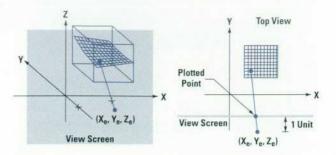

Given this unity of purpose, there is considerable overlap in the global parameters (options) used in these routines. These plotting parameters are stored in the variable VPAR, analogous to PPAR.<sup>3</sup> The main data structure stored in VPAR describes the *view volume*, a region in abstract three-dimensional space in which most of the visualizations occur (see Fig. 23).

VPAR quantities controlling the view volume are:

- X<sub>left</sub> and X<sub>right</sub>, controlling the width of the view volume

- · Yfar and Ynean controlling the depth of the view volume

- Zlow and Zhigh, controlling the height of the view volume

- X<sub>e</sub>, Y<sub>e</sub>, and Z<sub>e</sub>, the coordinates of the *eye point*.

In addition to these, VPAR contains other quantities used by some of the routines. These are:

- XX<sub>left</sub> and XX<sub>right</sub>, an alternative X input range, used for GRIDMAP and PARSURFACE

- YY<sub>far</sub> and YY<sub>near</sub>, an alternative Y input range, used for GRID-MAP and PARSURFACE (note that this differs from the current Suite3D interpretation)

- N<sub>x</sub> and N<sub>y</sub>, the number of X and Y increments desired, used in all of the routines instead of or in combination with RES.

#### SLOPEFIELD

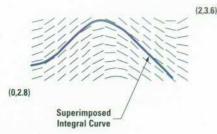

The SLOPEFIELD plot type draws a lattice of line segments whose slopes represent the function value at their center point. Using SLOPEFIELD to plot f(x,y) allows your eye to pick out integral curves of the differential equation dy/dx = f(x,y). It is quite useful in understanding the arbitrary constant in antiderivatives.

Fig. 23. VPAR parameters in relation to the view volume.

Fig. 24. SLOPEFIELD plot of dx/dt = sin(xt).

The number of lattice points per row is determined by  $N_x$  and the number of lattice points per column is determined by  $N_y$ . The input region sampled is given by  $X_{left}\!<\!X\!<\!X_{right}$  and  $Y_{near}\!<\!Y\!<\!Y_{far}$

The input form in this case allows the user to:

- Choose or enter the defining expression for the function to be plotted

- Choose the names of the two variables (identical to INDEP and DEPEND)

- Choose X<sub>left</sub> and X<sub>right</sub> (default to their current value, or XRNG if no current value)

- Choose Y<sub>near</sub> and Y<sub>far</sub> (default to their current value, or YBNG if no current value)

- Choose  $N_x$  and  $N_y$  (default to their current value or 13 and 8 if no current value)

- Verify and/or choose RADIANS, DEGREES, or GRADS mode.

In trace mode for SLOPEFIELD, the arrow keys jump the cursor from sample point to sample point indicating both the coordinates of the sample point and the value of the slope at that point.

**Example Problem**: Determine graphically whether all solutions of the differential equation dx/dt = sin(xt) with initial conditions 3.0 < x(0) < 3.1 satisfy 2.8 < x(t) < 3.6 for all t in [0,2].

**Solution**: Choose SLOPEFIELD plot type and enter SIN(X\*T) as the current equation. Choose T as the independent variable and X as the dependent variable. Choose 0 as  $X_{left}$ , 2 as  $X_{right}$ , 2.8 as  $Y_{near}$  and 3.6 as  $Y_{far}$ . Verify RADIANS mode, and draw the result. As seen in Fig. 24, almost all of the integral curves in this region leave the window either through the top or the bottom. Therefore, not all the integral curves satisfy 2.8 < x(t) < 3.6 for t in [0,2].

#### WIREFRAME

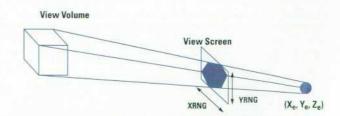

The WIREFRAME plot type draws an oblique-view, perspective, 3D plot of a wireframe model of the surface determined by z = f(x,y). The function determined by the current equation is sampled in a grid with  $N_x$  samples in each row and  $N_y$  samples in each column. Each sample is perspective-projected onto the view screen along the line connecting the sample and the eye point (see Fig. 25).

Neighboring samples are connected by straight lines. The sampled region is determined by the base of the view volume ( $X_{left}$ ,  $X_{right}$ ,  $Y_{near}$ ,  $Y_{far}$ ). The region of the view screen represented in the PICT GROB (graphics object<sup>3</sup>) and hence on the display is determined by the projection of the view volume on the view screen (see Fig. 26).

Fig. 25. Perspective projection of a point in the view volume onto the view screen.

The input form in this case allows the user to:

- Choose or enter the defining expression for the function to be plotted

- Choose the names of the two variables (identical to INDEP and DEPEND)

- Choose  $X_{left}$  and  $X_{right}$  (default to their current value, or XRNG if no current value)

- Choose Y<sub>near</sub> and Y<sub>far</sub> (default to their current value, or YRNG if no current value)

- $\bullet$  Choose  $Z_{low}$  and  $Z_{high}$  (default to their current value, or default YRNG if no current value)

- Choose X<sub>e</sub>, Y<sub>e</sub>, and Z<sub>e</sub> (default to their current value, or 0, -1, 0 if no current value)

- $\bullet$  Choose  $N_x$  and  $N_y$  (default to their current value or 13 and 8 if no current value)

- Verify and/or choose RADIANS, DEGREES, or GRADS mode.

In trace mode for WIREFRAME, the arrow keys jump the cursor from sample point to sample point and the display indicates all three coordinates of the sample point.

**Example Problem**: Determine graphically whether the surface defined by  $z = x^4 - 4x^2y^2 + y^4$  is, at the origin, concave up, concave down, or neither.

**Solution**: Choose WIREFRAME plot type and enter X^4–4\*X^2\*Y^ 2+Y^4 as the current equation. Choose X and Y as the independent and dependent variables. Choose –1 for X<sub>left</sub>, 1 for X<sub>right</sub>, –1 for Y<sub>neap</sub> 1 for Y<sub>fav</sub>, –1 for Z<sub>low</sub>, and 1 for Z<sub>high</sub> so that the view volume surrounds the origin. Choose 4 for X<sub>e</sub>, –10 for Y<sub>e</sub>, and 3 for Z<sub>e</sub> to give a distant, oblique view of the graph. As seen in Fig. 27, the graph displays a "monkey saddle" which is neither convex nor concave at the origin.

#### **New Interactive Features**

The picture environment, which is invoked automatically when graphs are drawn or by pressing the PICTURE key, allows the user to interact with a graph. The user can move

Fig. 26. Relationship of view volume and eye point to XRNG and YRNG.

Fig. 27. WIREFRAME plot of the surface determined by  $z = x^4 - 4x^2y^2 + y^4$  with view volume  $[-1,1]\times[-1,1]\times[-1,1]$  and eye point (4,-10,3).

the cross hairs around using the arrow keys, trace along the graph, add picture elements such as dots, lines, and circles, or do interactive calculus operations such as finding the derivative at the cross hairs location.

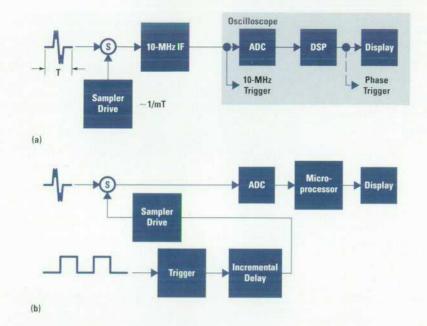

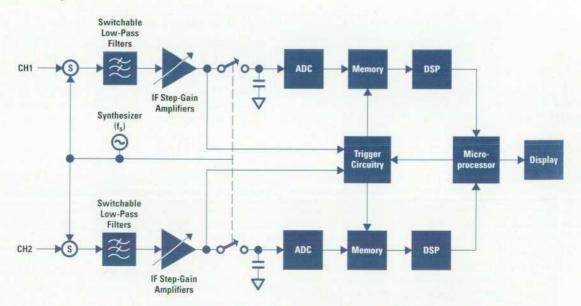

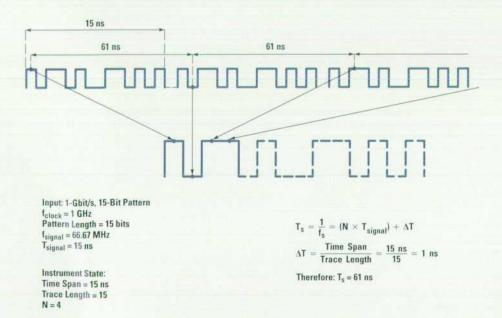

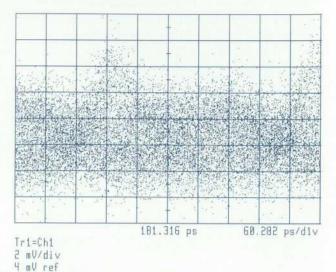

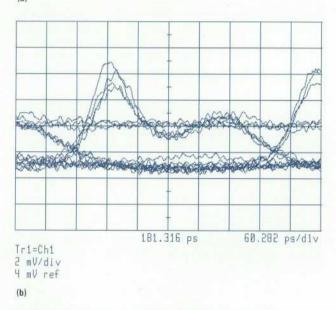

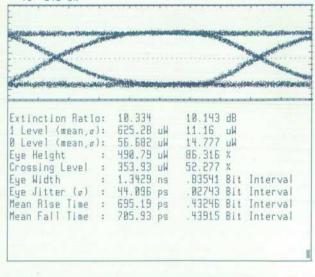

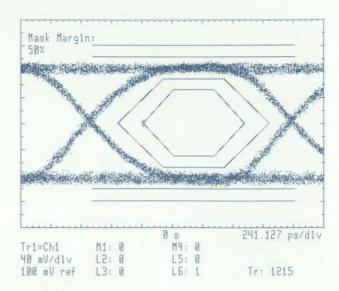

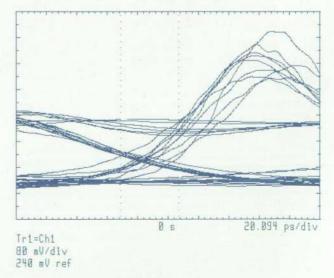

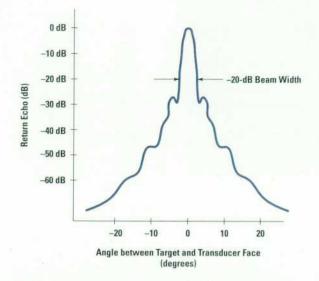

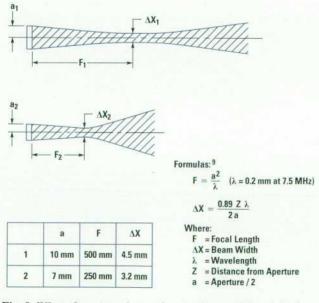

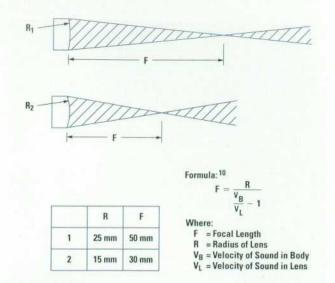

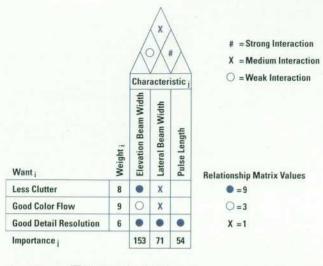

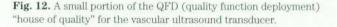

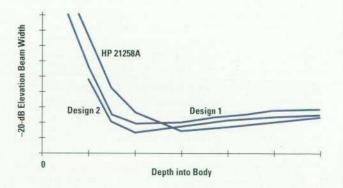

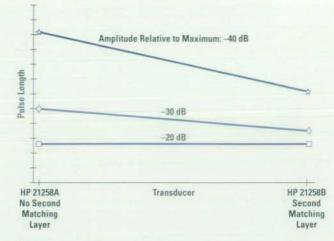

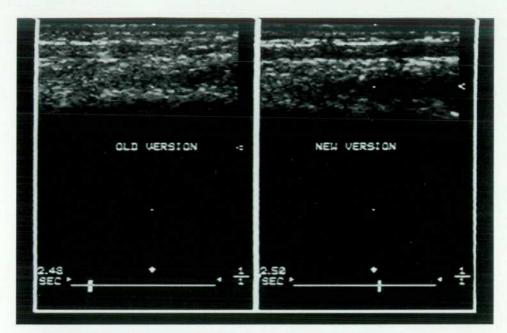

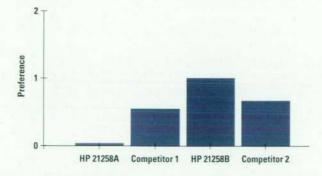

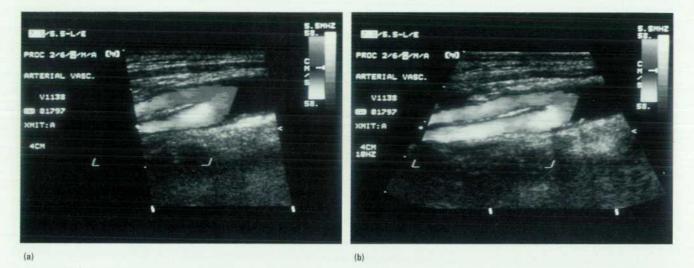

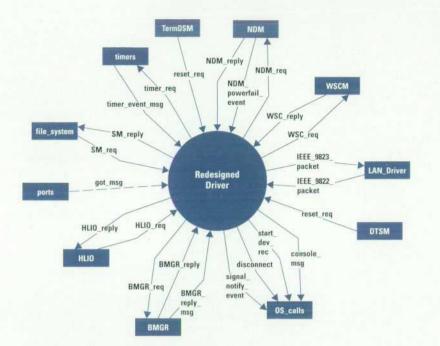

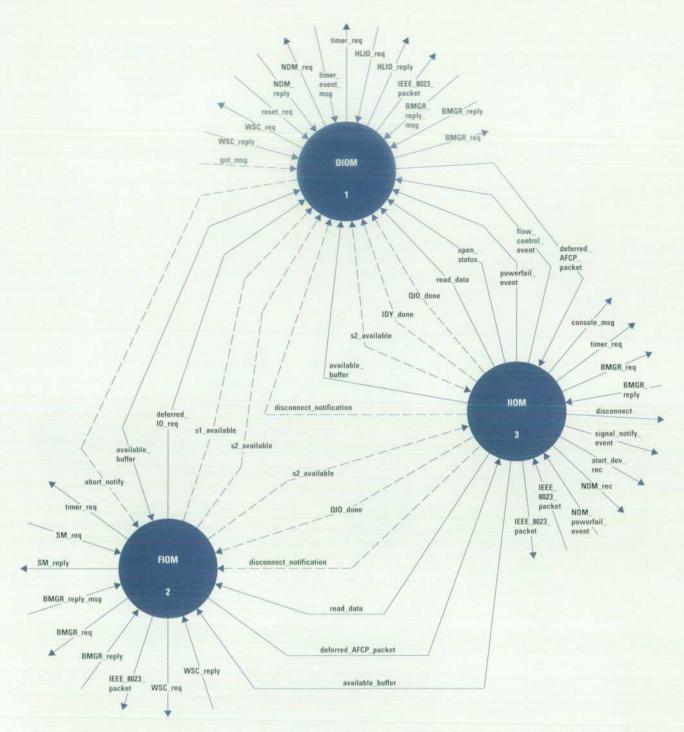

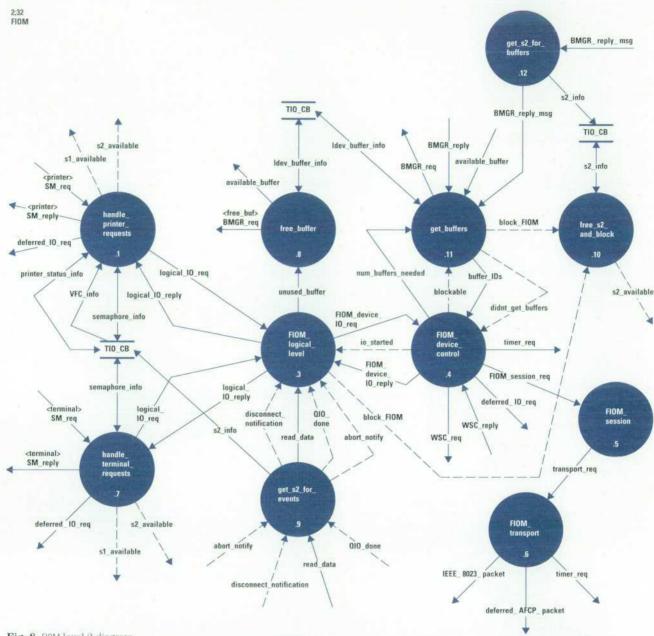

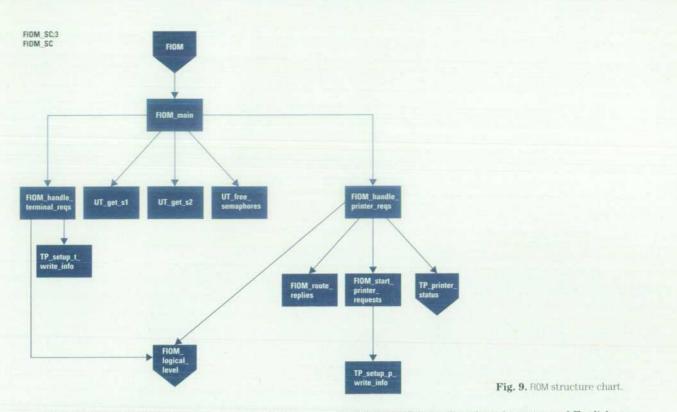

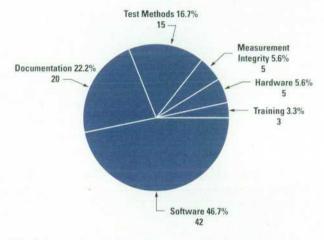

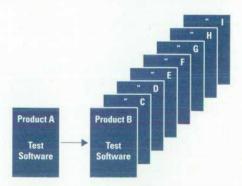

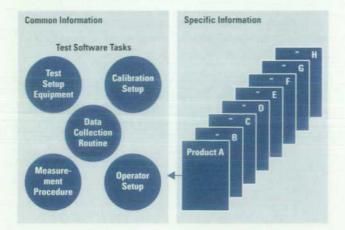

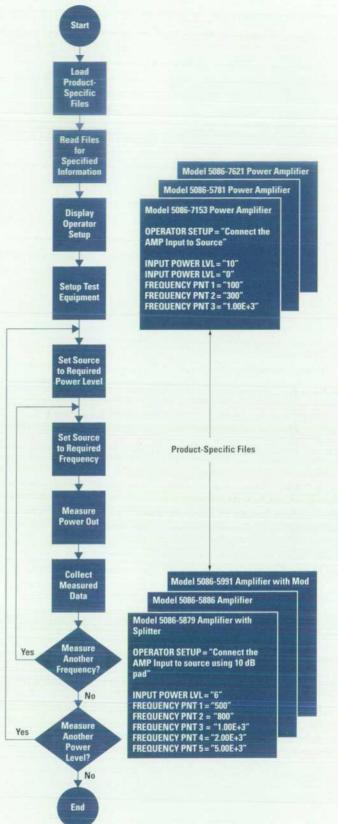

#### Trace, Faster Cross Hairs