# HEWLETT-PACKARD

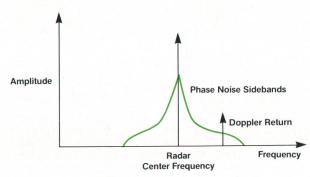

**DECEMBER 1987**

## HEWLETT-PACKARD

December 1987 Volume 38 ● Number 11

#### Articles

| 4 | Vector Si | gnal | Generation | and | Analysis, | by Allen P. | Edwards |

|---|-----------|------|------------|-----|-----------|-------------|---------|

|   |           |      |            |     |           |             |         |

- Hardware System Design for a Vector Analyzer, by Andrew H. Naegeli and Juan Grau

- 15 Quadrature and Phase Errors in Vector Demodulation

- 17 Firmware System Design for a Vector Analyzer, by Brian S. Messenger, Peter H. Fisher, and Stanley P. Woods

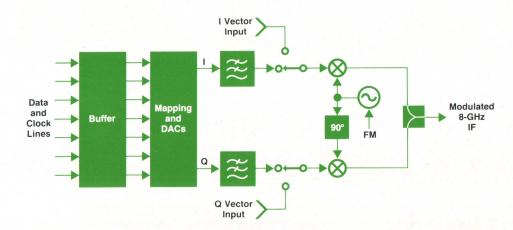

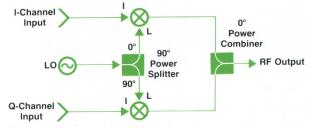

- Vector Modulation in a Signal Generator, by David L. Gildea and Donald R. Chambers

- 30 Firmware for a Vector Signal Generator, by James E. Jensen and Eric D. McHenry

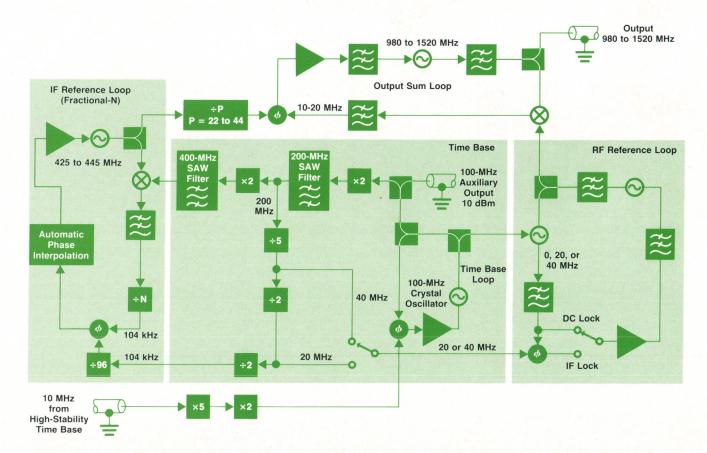

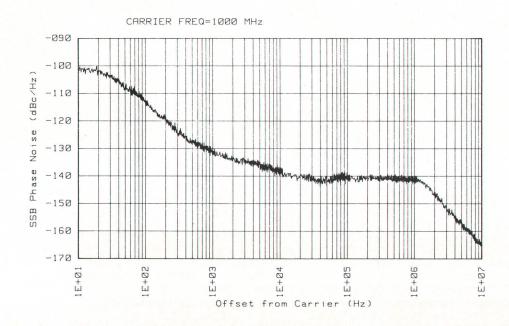

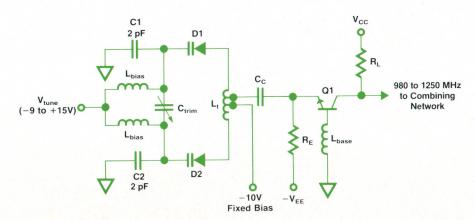

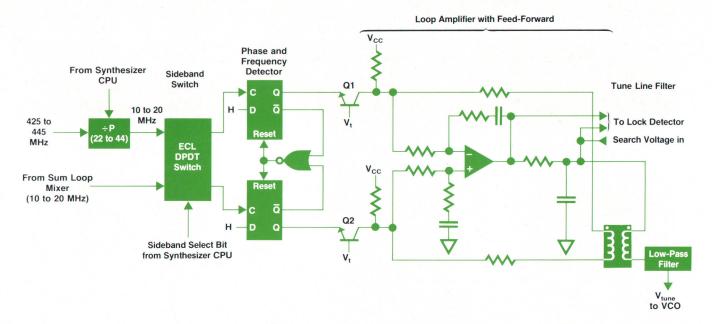

- 34 Low-Noise Synthesizer Design, by Thomas J. Carey, John C. Lovell, and Thomas L. Grisell

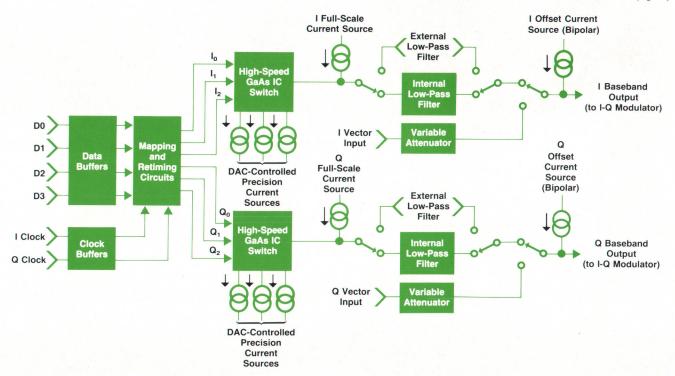

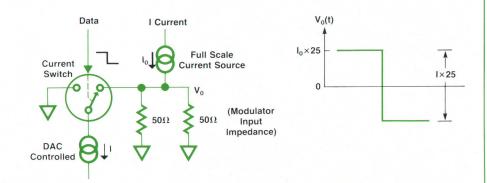

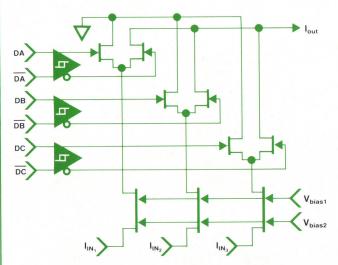

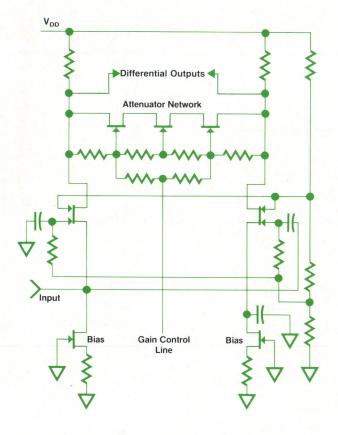

- Digital and Vector Baseband Circuits for a Vector Signal Generator, by Chung Y. Lau

- 41 A GaAs IC Current Switch

- 42 Describing Signals in the I-Q Domain

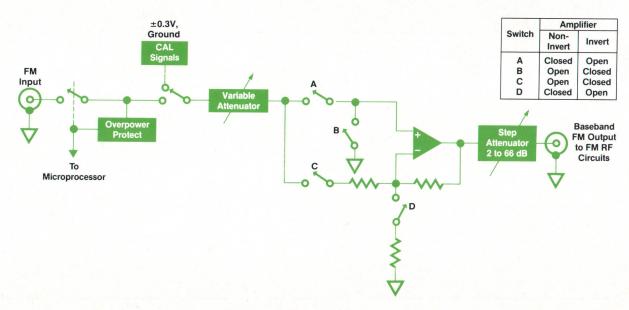

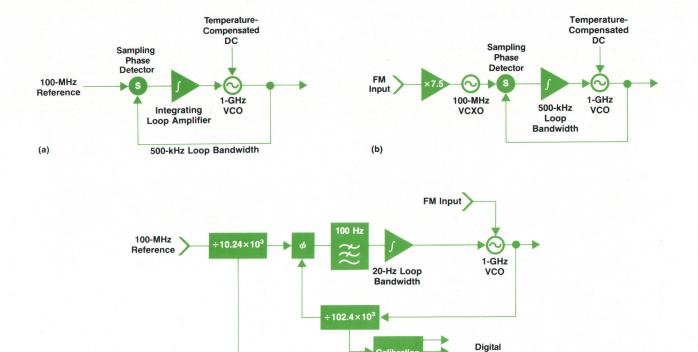

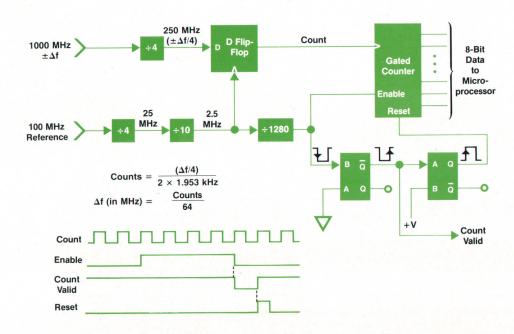

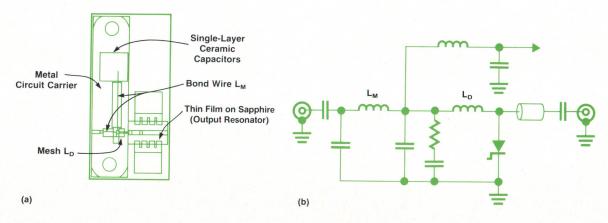

- 45 A Wideband FM Subsystem for a Low-Noise Synthesizer Module, by Eric D. McHenry

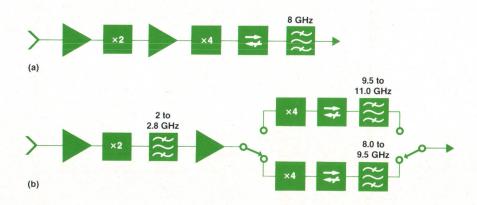

- Vector Modulator, Output Amplifier, and Multiplier Chain Assemblies for a Vector Signal Generator, by Wayne M. Kelly, Mark J. Woodward, Eric B. Rodal, Pedro A. Szente, and James D. McVey

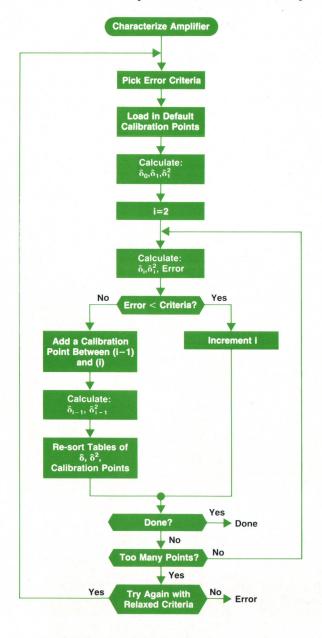

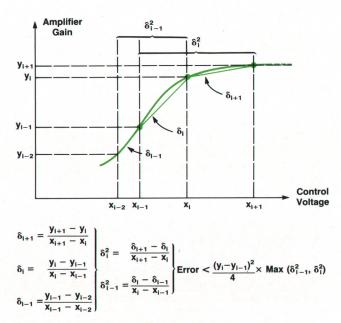

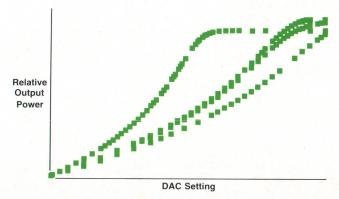

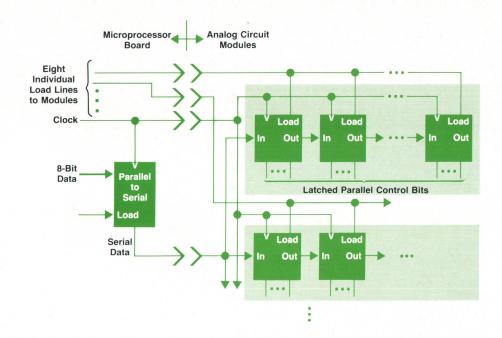

- 50 Baseband Calibration

- A Combinational Board Test System, by Michael E. Gravitz

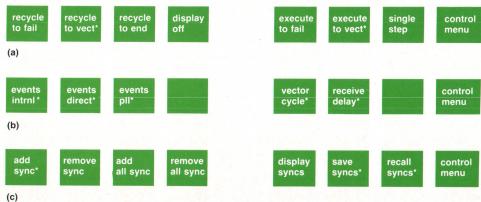

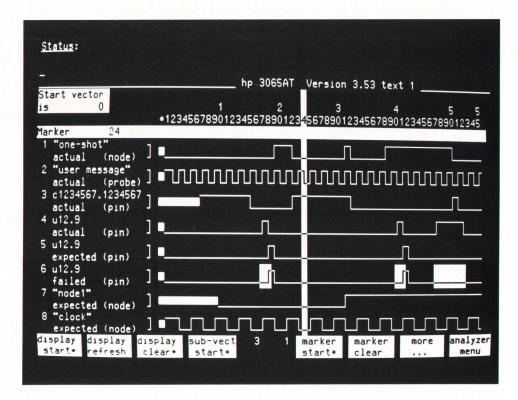

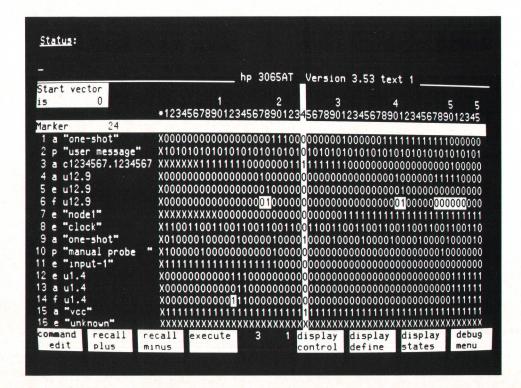

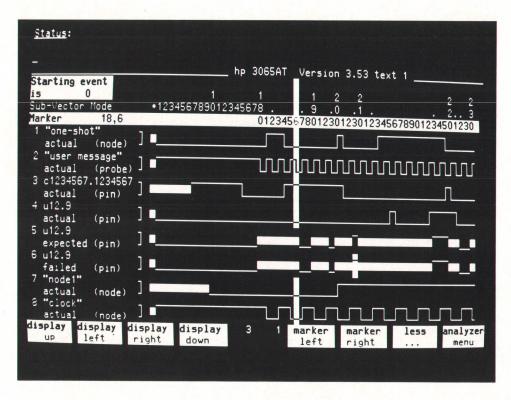

- 58 Interactive Graphical Debugging Package

- MPE XL: The Operating System for HP's Next Generation of Commercial Computer Systems, by John R. Busch, Alan J. Kondoff, and Darryl Ouye

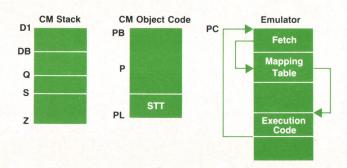

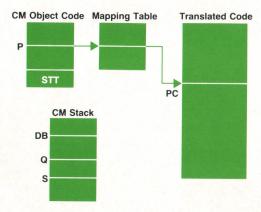

- HP 3000 Emulation on HP Precision Architecture Computers, by Arndt B. Bergh, Keith Keilman, Daniel J. Magenheimer, and James A. Miller

#### **Departments**

- 3 In this Issue

- 3 What's Ahead

- 65 Authors

- 90 Annual Index

Editor, Richard P. Dolan • Associate Editor, Business Manager, Kenneth A. Shaw • Art Director, Photographer, Arvid A. Danielson • Support Supervisor, Susan E. Wright Administrative Services, Typography, Anne S. LoPresti • European Production Supervisor, Michael Zandwijken

#### In this Issue

This is our first bimonthly issue. From now on, the Hewlett-Packard Journal will be published six times a year, in December, February, April, June, August, and October. Your comments on this change are welcome. December will continue to be the annual index issue; the 1987 index is on page 90.

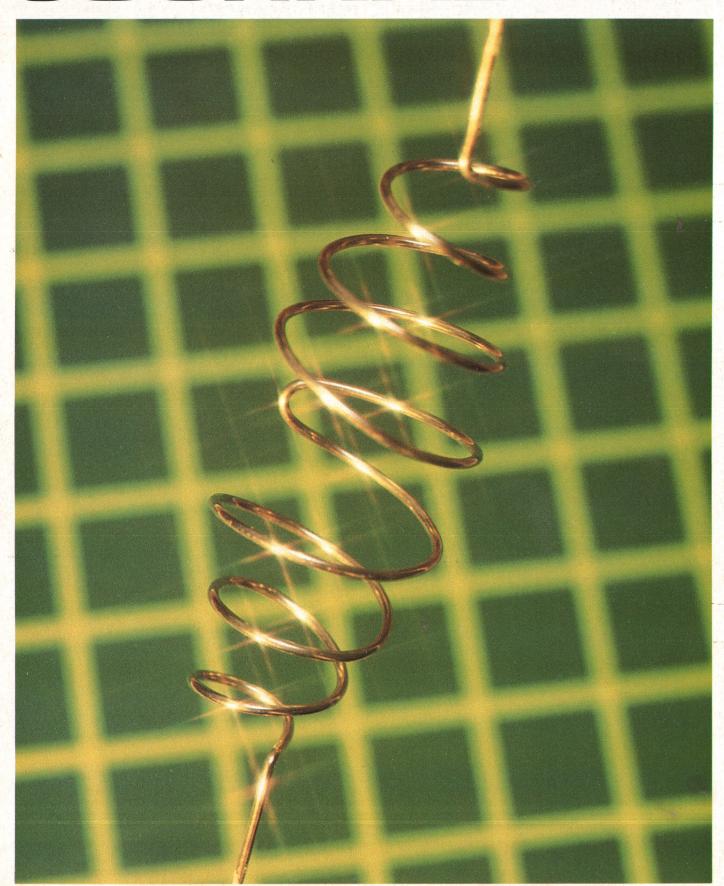

The cover photograph is of a three-dimensional model of a type of signal used in modern radar systems—the frequency chirp. The model is patterned after Fig. 12 on page 13, which shows HP 8980A Vector Analyzer displays of a rotated frequency chirp. The HP 8980A and the HP 8780A Vector Signal Generator are a pair of new instruments for testing digital radio, radar, and

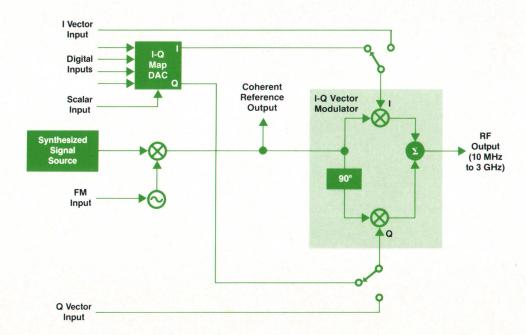

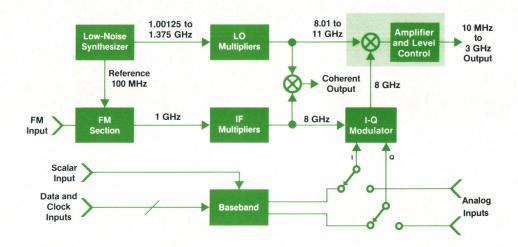

other systems that use vector modulation, a technique in which a carrier signal is modulated by one signal (I) and the same carrier shifted in phase by 90° is modulated by another signal (Q). The transmitted signal is the sum of the two modulated carriers. Vector modulation concepts are introduced in the article on page 4, and the designs of the HP 8780A and HP 8980A are described on pages 6 through 52. Among the design issues for the signal generator were the design of a low-noise carrier oscillator and the development of performance specifications and measurement methods in the absence of standards. The analyzer design provides two 350-MHz display channels, one for I and one for Q, along with several kinds of markers and measurement functions.

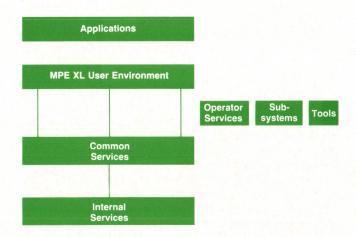

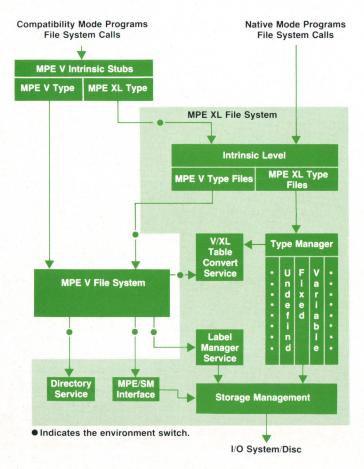

The Multiprogramming Executive, or MPE, is the operating system for the HP 3000 family of business computer systems. For the new HP Precision Architecture computers—the HP 3000 Series 930 and 950—MPE has been redesigned. MPE XL is a state-of-the-art operating system designed to realize the benefits of the architecture and provide a basis for future performance increases. Compatibility with previous MPEs and ease of migration to the new system for current users were major issues in MPE XL's development. In the file and transaction management systems, one of the key technologies is highly efficient support for mapped files, which allows megabytes of data to be accessed at main-memory speeds. The design of MPE XL is described in the paper on page 68. Compatibility features are discussed in more detail on page 87.

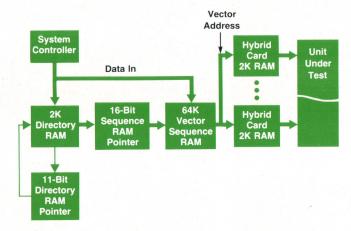

Very large-scale integrated (VLSI) circuits, application specific integrated circuits (ASICs), mixed analog/digital devices, and surface mount components are increasingly common in electronic manufacturing. To address the formidable testing problems posed by these devices and technologies, the HP 3065AT Board Test System has been developed. To the in-circuit tests of the earlier HP 3065 system, the HP 3065AT adds functional testing and new features to provide test engineers with new strategies and capabilities appropriate to the challenges they face. The HP 3065AT's design is the subject of the article on page 53.

-R.P. Dolan

#### What's Ahead

In the February issue, we'll have several articles on precision digitizing oscilloscope design based on waveform recorder technology. The products covered are the HP 5180T/U, 5183T/U, and 5185T Precision Digitizing Oscilloscopes. Also featured will be the HP Printed Circuit Design System software, and silicon-on-insulator (SOI) technology.

## **Vector Signal Generation and Analysis**

This issue contains several articles describing the development of the HP 8780A Vector Signal Generator and the HP 8980A Vector Analyzer. To appreciate the nature of these products it is useful to discuss some of the concepts of vector modulation and its applications.

by Allen P. Edwards

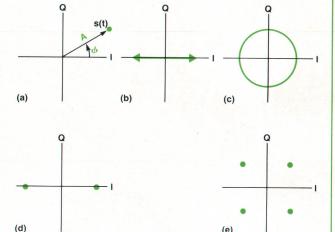

ODULATION refers to the modification over time of some property of a signal. The modification can be of the signal's amplitude, as in AM or amplitude modulation. It also can be the change of some other property as in frequency modulation (FM) or phase modulation (PM). Signals are typically modulated for the purpose of encoding some information on the signal. This information may be in the form of voice, text, or in the case of radar signals, time (which is interpreted as distance or range).

In the last few years some modulation schemes particularly suited to digital communications have become increasingly important. One of the first of these is phase-shift keying (PSK). PSK can be thought of as digital phase modulation in which there is a fixed set of valid phases. In the case of 4PSK (QPSK) there are four phases spaced 90 degrees apart. Each valid signal location is called a signal state and in the case of QPSK, there are four states. The signal changes state in response to digital inputs. The signal will transition between the states in the shortest path, which is not the path of constant amplitude. Thus, PSK causes both amplitude and phase variation in the signal unlike conventional phase modulation which is confined to constant amplitude.

Another popular form of modulation is quadrature amplitude modulation (QAM). In this form of modulation two orthogonal carriers (sine and cosine components of a reference phase) are independently modulated to form n valid amplitude levels or states. The two components are considered the I (in-phase) and Q (quadrature) channels. The composite signal has  $n^2$  states that form a rectangular pattern of dots when viewed in a graph of I versus Q. (This pattern is called a constellation diagram.) This modulation has multiple levels and phases, but just n I levels and n Q levels. Some examples are 16QAM (4×4) and 64QAM (8×8).

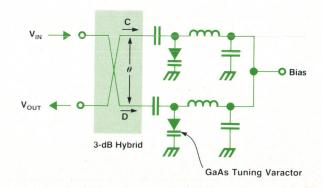

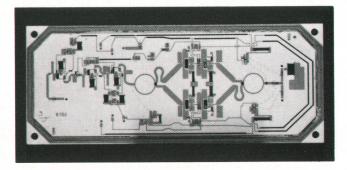

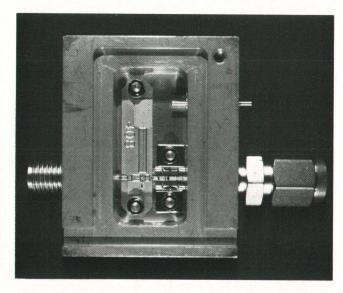

#### **Vector Modulation**

Vector modulation is simply the description of a modulation in terms of its I and Q components versus time. It can be used to describe all types of modulation, but is most useful in describing the rectangular modulations, which include AM, PSK, QAM, and pulse. It also can be extremely useful for analyzing FM and PM as well.

Vector modulation can be described by an equation with the form:

$s(t) = i(t)\sin(\omega t) + q(t)\cos(\omega t)$

This equation describes QAM modulation exactly. Let's see how it can also describe other types of modulation as well.

Amplitude Modulation:  $s(t) = a(t)sin(\omega t)$ . Modulate the in-phase component with the desired modulation i(t) = a(t) and set the quadrature term q(t) to zero. Note that this equation also applies to pulse modulation.

**Phase Modulation:**  $s(t) = \sin(\omega t + \phi(t))$ . Represent s(t) as

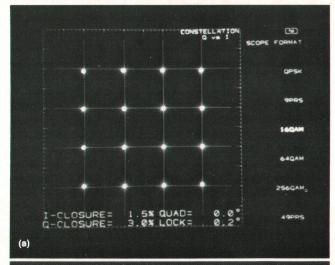

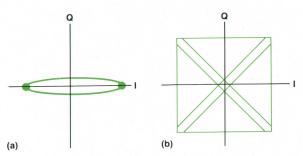

**Fig. 1.** Constellation diagram of a 16QAM radio (a) using the radio as a reference and (b) as it actually should look.

the sum of its two rectangular components using  $\sin(a+b) = \cos(b)\sin(a) + \sin(b)\cos(a)$ . Therefore,  $i(t) = \cos(\phi(t))$  and  $g(t) = \sin(\phi(t))$ .

Vector representation has a distinct advantage in describing modulation in that the representation is linear. Phase modulation has the problem that it is nonlinear (this is why Bessel functions often come up in its description). Vector representation is particularly useful in describing what happens when the modulation is passed through a filter. In the case of the traditional phase modulation description, RF filtering adds harmonic terms to the description. In the I-Q representation of phase modulation, RF filtering removes terms. Also, the effects of filtering on RF and baseband are equivalent in I-Q modulation where they are not in phase modulation.

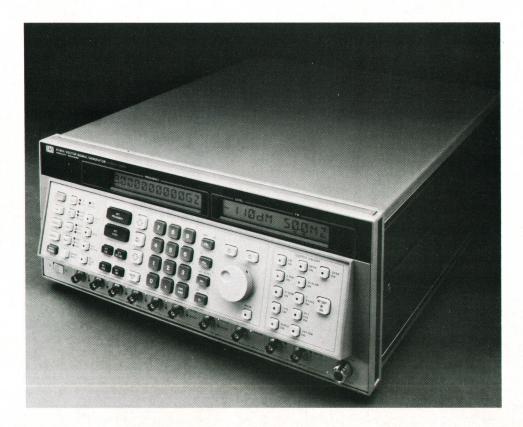

The HP 8780A Vector Signal Generator is an IF and RF signal generator that covers an output frequency range of 10 MHz to 3 GHz. It provides a rich assortment of modulation types to the user as described in the articles on pages 25, 39, and 45. They include:

- FM: both wideband (FDM/FM and FMTV) and narrow-band (low phase noise)

- Digital modulation: pulse, BPSK, QPSK, 8PSK, 16QAM, 64QAM, and others

- Analog vector modulation: I and Q inputs to 350-MHz bandwidth

- AM available either as a vector modulation input (350-MHz bandwidth) or on top of the digital modulation formats (to simulate fade). This AM has low phase noise consistent with the application's requirements.

#### **Vector Analysis**

The HP 8980A Vector Analyzer is basically a two-channel sampling oscilloscope with features designed for analysis of the I and Q outputs of a radio or demodulator. It has 350 MHz of X-Y (called I-Q) bandwidth. This allows the user to view repetitive events in the I-Q plane in real time. The HP 8980A is fully programmable. It has many measurements, markers, and features designed to make it easy to analyze modulated signals.

The HP 8780A and HP 8980A represent a new generation of signal generation and analysis products. They are required by the reality that users are no longer working with voice and simple pulse in their microwave applications. Digital modulation is a requirement in communications and radar applications of signal generators. Higherbandwidth FM also is a requirement for communications and radar (wideband chirps are possible over more than 100 MHz with the HP 8780A). The analysis of these signals requires a fully programmable HP-IB (IEEE 488/IEC 625), high-bandwidth (350 MHz), high-resolution (up to 12-bit resolution) capability. The HP 8980A offers this.

Fig. 2. Recommended test setup for obtaining the correct constellation diagram of a 16QAM radio.

#### **Applications**

In the area of digital radio (both satellite and terrestrial), the two products work together to test receivers. The HP 8780A serves as a calibrated transmitter with known and specified accuracy. This avoids the problem with homebuilt solutions created by unknown errors in the transmitter that mask and cancel the errors in the receiver. Fig. 1 shows the constellation diagram of a 16QAM radio as seen by a receiver that was adjusted with the radio as a reference and the constellation as it actually should look. A recommended test setup is shown in Fig. 2. As can be seen, a markedly out of adjustment radio may look good if not measured with a calibrated transmitter. In addition, homebuilt solutions have the hidden cost of developing NBS traceability, documentation, and supportability that always makes them more expensive than they are expected to be.

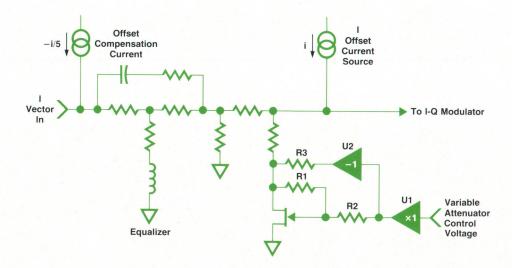

Another application uses the HP 8780A Vector Signal Generator as a calibrated standard to calibrate a demodulator for use as a test demodulator. The HP 8980A Vector Analyzer has built-in features that allow the compensation of external demodulator quadrature and phase errors as well as the more obvious offsets and gains.

Some other applications in radar testing include module testing, transient testing, time delay testing, and image rejection. These applications require coded pulses and the formation of extremely fast pulses or shaped pulses. With a minimum rise time of 1 ns and the ability to have baseband pulse-shaping filters, a wide variety of pulses can be formed by the HP 8780A. The FM deviations available in the generator allow chirp FM deviations. The combination of a calibrated demodulator, the HP 8980A, and a calculator allow the analysis of instantaneous frequency versus time in a chirp pulse.

## Hardware System Design for a Vector Analyzer

by Andrew H. Naegeli and Juan Grau

O MEASURE THE PERFORMANCE of many modern microwave systems, it is necessary to measure the instantaneous amplitude and phase of an RF signal. Digital radio systems, for example, use complex modulation signals that convey information in both amplitude and phase, and at very fast rates. Modulation rates of 60 megabaud and higher are common.

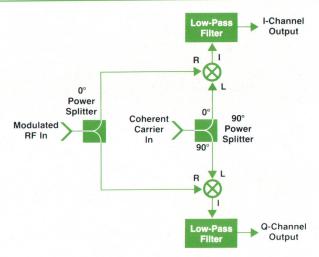

Most systems of this type use vector demodulation (also called I-Q demodulation, coherent detection, or quadrature detection) to recover the in-phase (I) and quadrature (Q) components of the signal. These in turn are used to detect the items of interest in the system. For example, the data decisions are made from the I and Q signals in QPSK (quadrature phase-shift keying) digital radios.

The HP 8980A Vector Analyzer (Fig. 1) is designed to measure instantaneous amplitude and phase of wideband RF and microwave signals by analyzing their I and Q components in the time domain. It is a fully programmable HP-IB (IEEE 488/IEC 625) instrument designed for R&D and production applications.

The amplitude and phase of a signal can be analyzed visually by plotting the Q component versus the I component graphically in Cartesian coordinates. The amplitude is then represented by the distance from the center of the plot and the phase is represented simply by the angle thereon. The polar displays of vector network analyzers work on this same principle.

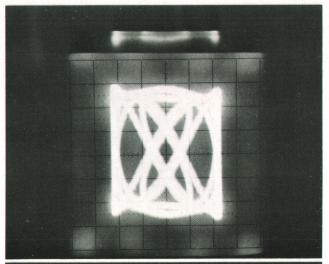

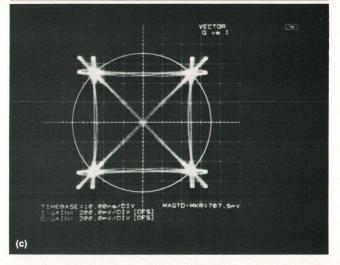

Accurately displaying the I and Q signals from wideband systems is not so easy, however, because of the large bandwidth of the signals. Most analog display instruments have a limited bandwidth in the X axis. Typically the 3-dB bandwidth of conventional oscilloscopes is about 5 MHz in the X-axis, even if the Y-axis bandwidth is 200 MHz or more. This results in distortion of the vector display when fast signals are analyzed, as shown in Fig. 2. To overcome

this difficulty the HP 8980A Vector Analyzer uses a sampling display system, with identical samplers in the I and Q channels. This technique provides identical wideband performance in both channels, where the bandwidth is set by the 1-ns rise time of the sampler circuits.

Using a sampled system also allows display of the constellation of a digital modulation signal. In a constellation display, the amplitude and phase states are viewed at a single time instant, which corresponds to the data decision sampling instant in a digital radio.

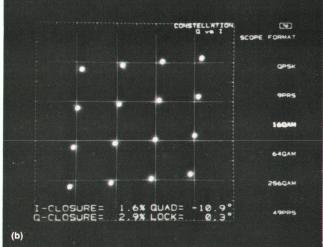

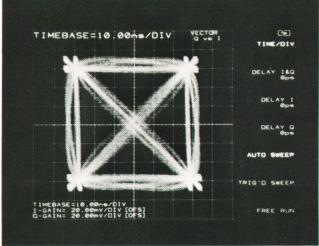

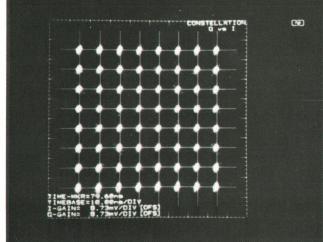

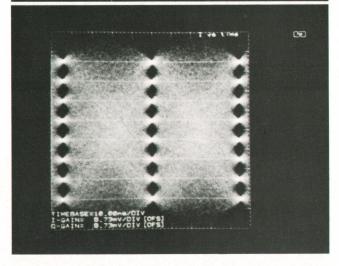

In addition to vector and constellation displays, the I or Q components can be displayed versus time for pulse timing measurements or for viewing eye patterns in digital radios. The timing is set like an oscilloscope, with time per division from 0.5 ns/div to 2 ms/div and delays up to 20 ms. Fig. 3 shows the vector and constellation displays of a 64QAM digital radio, as well as the I-versus-time display, which shows the eight-level eye pattern characteristic of this format.

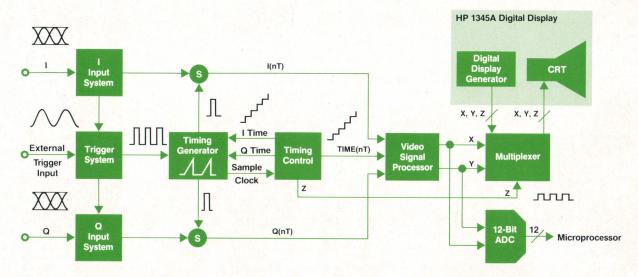

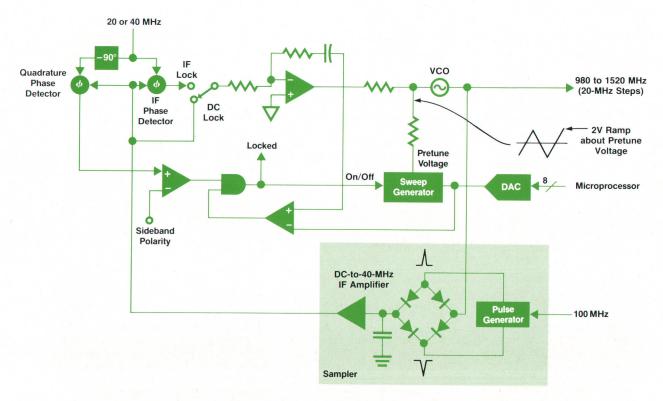

#### **Block Diagram**

A block diagram of the HP 8980A is shown in Fig. 4. The instrument uses an analog CRT display to provide higher-quality vector and eye displays than a digital display system would give. The analog system can process data at a much faster rate, up to one million samples per second in this case, compared to about 20 thousand in a digital display. In addition, the analog display provides information in the intensity of various parts of the displayed wave, so the relative density of different transitions in a complex waveform can be determined visually.

Many digital display features are included also, like a selection of grids, markers, and text. These are made possible by the digital stroke generator circuit, which is part of a specially modified version of the HP 1345A Digital

Fig. 1. The HP 8980A Vector Analyzer is a 350-MHz two-channel X-Y sampling oscilloscope designed to characterize the inphase and quadrature components of modern communications and radar system signals.

**Fig. 2.** (Top) The narrower bandwidth of the X axis in conventional oscilloscopes distorts the X-Y display of wideband data. (Bottom) HP 8980A display.

Display. This CRT display system is included in the HP 8980A as a replaceable module. Digital inputs to the HP 1345A are sent on a 26-pin cable from the microprocessor controller. This system provides very powerful display control for displaying menus, markers, help text, and various user messages.

The X, Y, and Z outputs of the digital stroke generator are multiplexed with the X, Y, and Z outputs of the analog display system to display the analog and digital information together. The multiplexing is done on a printed circuit board outside the display module and the signal is sent back into the display module just before the deflection plate amplifiers. The relative timing of the refreshing of the digital information and the display of the analog signals is a complex process. This process is discussed in the article on the firmware design for the HP 8980A on page 17.

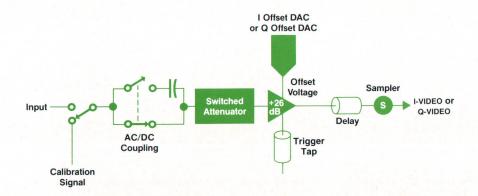

#### I and Q Input System

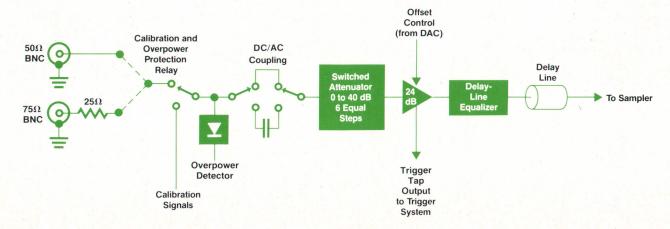

The I and Q inputs are processed before sampling by the system shown in Fig. 5. The input impedance is selected by using interchangeable BNC connector and series resistor

Fig. 3. Vector (top), constellation (middle), and eye (bottom) displays for 64QAM radio.

assemblies on the front panel. The 75-ohm connector uses a 25-ohm series resistor to bring the 50-ohm impedance of the rest of the instrument up to the 75-ohm level. The 50-ohm input connector uses a conductor in place of the series resistor. These assemblies are screwed into a socket

Fig. 4. System block diagram.

on the front panel for easy reconfiguration. The 75-ohm assembly has an attenuation factor of 1.5 because of the resistive divider, and this reduces the sensitivity of the instrument from 5 mV/div to 7.5 mV/div. This division factor can be accounted for in the gain and offset setup functions by selecting 75 ohms in an instrument state configuration menu.

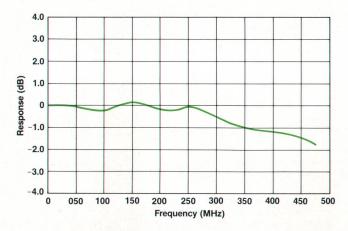

The first input relay is used for switching in calibration signals and for opening the inputs when an overpower signal is detected by the detector. Ac coupling is selected by switching in a capacitor. The switched attenuator is used to scale the signal into the amplifier and sampler in coarse steps for optimum distortion and noise performance. The dc-to-500-MHz amplifier is built in surface mount technology for better RF performance than is possible with a standard printed circuit design. The amplifier has an offset control input for up to one full scale of offsets and a trigger output that is isolated from the signal output. The equalizer corrects the pulse distortion and poor frequency response of the coaxial delay line before the samplers. The delay line is required to view the signal at the trigger instant, since the trigger and timing systems take several

nanoseconds to generate a sampling pulse.

#### Samplers

The samplers perform the function of compressing the 350-MHz input bandwidth into a video bandwidth of about 3 MHz. This allows the display unit with its limited bandwidth in the X and Y axis to handle the kind of signals that are likely to be encountered in modern communications and radar systems. To reproduce the input signals accurately in the video range (the postsampler signals are referred to as video signals), the samplers are driven by the timing generation block and the timing control block (Fig. 4). They use a variation of a timing technique called sequential sampling which takes advantage of the fact that the signals under observation are repetitive in nature (more on this in the timing section).

To have a total system bandwidth of 350 MHz, each band-limiting element in the chain must be able to accommodate bandwidths greater than this. In this case the samplers are required to provide a bandwidth greater than 500 MHz. In addition to bandwidth goals, the samplers are required to hold samples for very long periods of time.

Fig. 5. Block diagram of I (or Q) input system.

Fig. 6. Sampler schematic.

This allows the internal voltmeter enough time to complete the analog-to-digital conversion required in several of the internal measurement functions (calibration, print, HP-IB data query, constellation measurements, etc). It is very difficult to build a sampler that satisfies both of the above requirements in a single stage, that is, one with very wide input bandwidth and long hold time simultaneously. Therefore, we opted to split the task in two separate sampler circuits. The first sampler circuit provides the bandwidth while the second circuit handles the long hold times. The conversion time of the analog-to-digital converter (ADC) is approximately 25  $\mu$ s per point, which for two channels plus overhead translates into hold times of over 100  $\mu$ s.

The design of the second sampler is rather straightforward since it deals only with signals within the system's video bandwidth. In deciding the topology for the first sampler a few more issues had to be considered. Two sampling technologies are widely used at the present time: sample-and-hold or track-and-hold. We chose the track-and-hold technique because of better noise and distortion performance while providing sufficient bandwidth performance to satisfy our requirements. Using printed circuit board technology and state-of-the-art components, this circuit pushes to the limit the bandwidth performance of a track-and-hold design. Wide bandwidths are much more easily attained in sample-and-hold designs but noise, distortion, and sampling efficiency issues steered us away from using sample-and-hold techniques.

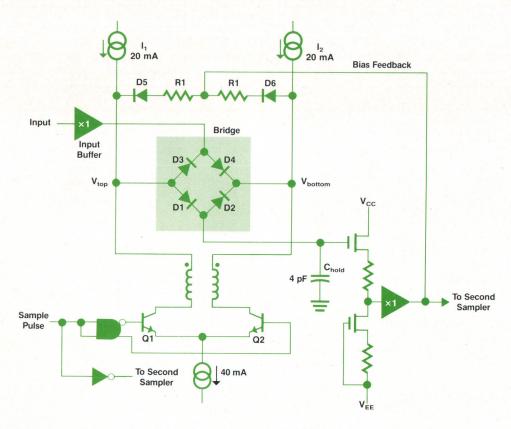

Fig. 6 shows a simplified schematic diagram of the first sampler. During track mode, transistor Q2 is on and Q1 is off. Since Q1 is off, the current from current source I1 only has one way to go—through the diode bridge, turning it

on. While in this state the bridge behaves as a resistor equal to the dynamic resistance of one diode at the particular bias current. Since the load is capacitive, only at high frequencies is there any significant signal current flowing through the bridge. This means lower distortion at the lower frequencies. The voltage on  $C_{\rm hold}$  ideally follows the input voltage within the bandwidth of the low-pass filter created by the bridge resistance ( $R_{\rm bridge}$ ) and  $C_{\rm hold}$ . In reality parasitic and various FET-related capacitances in combination with trace inductances contribute as much to limiting the bandwidth as  $R_{\rm bridge}$  and  $C_{\rm hold}$  do. The input buffer serves two purposes: to provide reverse isolation to keep current spikes related to the sampling pulses from going out of the circuit board and to present a low-impedance drive for the bridge.

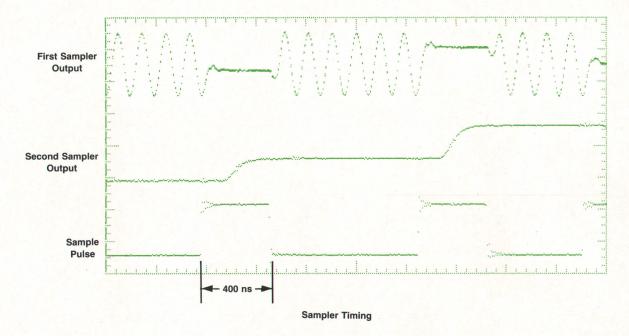

When the sampler goes into hold mode, transistor Q1 turns on and Q2 turns off. I1 flows directly into the collector of Q1 while I2 finds its way through D5 and D6. This current results in a voltage drop from the cathode of D2 to the anode of D1, reverse-biasing the diode bridge. During this transition the current in the diode bridge goes from 20 mA in its on state to zero current in the off state in a few hundred picoseconds, the time that the bridge takes to go from its low-impedance state to its high-impedance state. While the charge is being held in the first sampler, the second sampler acquires this voltage (see Fig. 7). When the first sampler returns to the tracking mode, the second sampler in turn goes into its hold mode, retaining the sampled voltage for further video processing.

The secret to achieving good distortion performance in this circuit is balance. Several things are done to ensure balance in the bridge's driving signals. To begin with, the

Fig. 7. Sampler waveforms.

diode bridge design is monolithic, which provides a good match between all four diode characteristics as well as their parasitic capacitances. The balun transformer at the collectors of the switching transistors helps ensure that the drive signals at the top and bottom of the bridge are complementary by presenting a high impedance to common mode signals from Q1 and Q2, but a low impedance to the differential mode signals. If symmetry in these waveforms were not maintained, the balance in the currents through the individual bridge diodes would be disrupted, resulting in distortion.

Another distortion-fighting mechanism in the circuit is the bias feedback loop. When the bridge makes the transition from on to off, a reverse voltage equal to two diode drops (D5 and D6) plus the IR drop in R1, appears across the bridge. The simple approach would be to ground the bias feedback node. This would be enough to ensure that the bridge is turned off over a range of  $C_{\rm hold}$  voltages of about  $\pm 1.5 V$ . In this case, the voltages across the bridge diodes D1 and D2 would be:

$$V_{D1} = V_{C_{hold}} - V_{top}$$

$$V_{D2} = V_{C_{hold}} + V_{bottom}$$

where  $V_{\rm top}$  would be about 1.5V below ground and  $V_{\rm bottom}$  the same amount above ground (R1 = 50 $\Omega$ ). Hence, the voltage across D1 and D2 would be a function of the sampled voltage  $V_{C_{\rm hold}}$ . However, the diode bridge has parasitic capacitances that are significant compared to the hold capacitor and that are nonlinear with voltage. These capacitances suck up a proportion of the charge originally trapped in  $C_{\rm hold}$  as reverse voltage develops across them, changing the voltage held by  $C_{\rm hold}$ . Since the voltage across the bridge diodes is in this case a function of the sampled voltage itself, the nonlinearities in the parasitic capacitances would

result in nonlinear redistributions of charge among the three capacitances in question. This would show up as distortion. To get around this problem, the feedback node is tied to the buffered version of the  $C_{\rm hold}$  voltage. This ensures that the potential developed across the parasitic capacitances during the hold period is constant and not dependent on the sampled voltage. This greatly reduces distortion effects caused by the nonlinear capacitances of the sampling bridge.

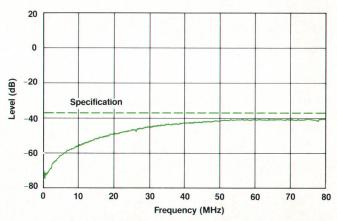

The most significant distortion mechanism left in the circuit is that caused by slew rate limiting. The 20-mA maximum current that the bridge can supply acts as a limit on dV/dt in  $C_{hold}$ . With the bias currents chosen, this sampler is able to keep distortion terms less than  $-40~\mathrm{dB}$  at

Fig. 8. Video signal processing block.

frequencies greater than 150 MHz. At low frequencies the distortion is less than -60 dB (for a 1V signal), essential in meeting the system's dc accuracy goals.

#### **Video Signal Processing**

After the samplers capture the data, some video processing is needed to condition the signal before it can be shown on the display unit. Some of the functions required are fine gain adjustment, position control, and signal routing to produce the several types of displays the HP 8980A is capable of displaying. For example, it may be necessary to route the Q-channel information to the Y axis of the CRT and the sweep information to the X axis to display Q versus time (this is the regular oscilloscope mode). On the other hand, for a vector display (the equivalent of X versus Y mode on scopes) the I-channel samples should be sent to the X axis instead.

In addition to the functions mentioned above, the video processing block performs certain kinds of linear operations needed to implement the quadrature and phase correction features of the instrument (see box on page 15). An extension of this capability is the 3-D display which will be discussed later.

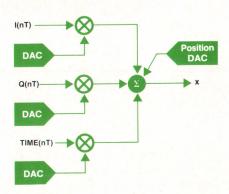

The basic function of the video block can be described by the following matrix operation:\*

$$\left[\begin{array}{c} X \\ Y \\ Z \end{array}\right] = \left[\begin{array}{ccc} a_1 & a_2 & a_3 \\ b_1 & b_2 & b_3 \\ x & x & x \end{array}\right] \left[\begin{array}{c} I(nT) \\ Q(nT) \\ \text{TIME}(nT) \end{array}\right]$$

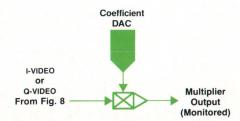

The last row of the matrix is filled with xs (don't cares) because only the X and Y information is ever needed for display (in this case, the Z axis of the CRT is driven by a separate circuit). Fig. 8 shows a simplified block diagram of this circuit. When a user chooses a setting, the microprocessor calculates the matrix coefficients corresponding to it. The video block then performs the remaining multipli-

<sup>\*</sup>The timing signal TIME is the sweep control voltage generated in the timing control block. In addition to telling the timing generation circuits when to sample with respect to the trigger event, the TIME signal also tells the CRT display where along the X axis that sample should be positioned.

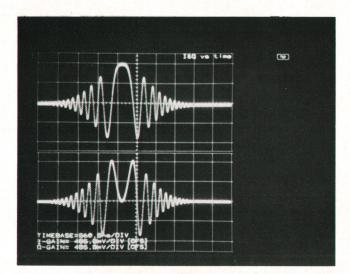

Fig. 9. Chirp Q and I components versus TIME.

cations and additions needed to complete the matrix operation. The multiplications and additions are done in the analog domain to achieve the data processing speed required by the system, which can be as fast as one megasample per second in some instances. The fast data throughput is needed to display the large amounts of information contained in some signals used in the digital communication field (e.g., eye and vector diagrams of higher-order modulation formats). To try to achieve this data update rate digitally would have resulted in a much more expensive and complex circuit. This way the task is split between the microprocessor and the analog circuits.

The processor calculates the matrix coefficients, which depend on the setup of the instrument. This computation can be time-consuming because it involves complex trigonometric functions. Fortunately, users do not require the ability to change setups (like sensitivity or display mode) very fast. Update rates of three or four times per second will satisfy most needs. This provides the software with enough time to do the necessary math. Once the coefficients are programmed, the analog circuits can do the remaining processing of the samples at blazing speeds (relatively speaking).

Consider a simple case—the vector display, where the Q-channel data is displayed on the Y axis and the I-channel data is displayed on the X axis of the CRT. The processor sets the matrix coefficients as follows:

$$\left[\begin{array}{c} X \\ Y \end{array}\right] \ = \ \left[\begin{array}{ccc} 1 & 0 & 0 \\ 0 & 1 & 0 \end{array}\right] \ \left[\begin{array}{c} I(nT) \\ Q(nT) \\ \text{TIME}(nT) \end{array}\right]$$

If the fine gain needs to be adjusted, the firmware changes the ones to fractions of one, resulting in a sensitivity change.

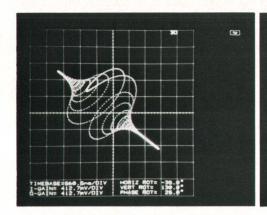

The several kinds of displays that have been described so far are two-dimensional in nature. The Q and I channels are displayed versus each other or versus time. Fig. 9 shows a display of both channels versus time for a signal typically used in modern radar systems, the frequency chirp. A chirp

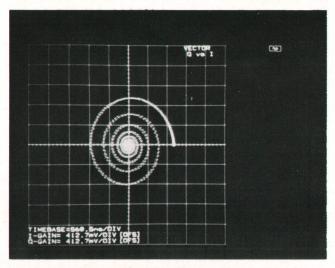

Fig. 10. Chirp Q versus I display.

is a signal whose frequency varies linearly with time. In most practical cases its amplitude is also modulated to provide timing references from which to measure radar returns. Fig. 10 shows the same chirp but this time one channel is plotted versus the other one. In this vector display phase and amplitude information can be extracted from the polar interpretation of the screen. The spiral trajectory tells us that as the phase changes with time so does the amplitude. The exact time dependency of this change is not as evident from this display as it is when plotted versus time.

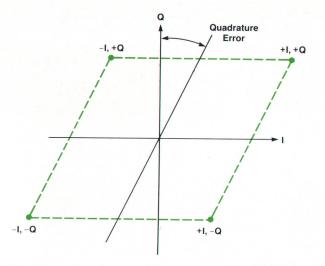

By viewing the operation performed by the matrix as merely a mapping from one space (call it the signal space) to another (the display space), and recognizing that the video processing circuit is capable of setting the matrix coefficients arbitrarily (within the 12 bits of the digital-to-analog converters), one can consider a whole new set of interesting possibilities. Two HP 8980A functions that make use of this capability are the phase and quadrature correction algorithms (see box on page 15). The phase correction is a mapping that rotates the I-Q signal space about the origin. This operation is described by the matrix:

$$\left[\begin{array}{c} X \\ Y \end{array}\right] \ = \ \left[\begin{array}{ccc} \cos\theta & -\sin\theta & 0 \\ \sin\theta & \cos\theta & 0 \end{array}\right] \ \left[\begin{array}{c} I(nT) \\ Q(nT) \\ TIME(nT) \end{array}\right]$$

Quadrature errors are deviations from a perfect 90-degree relationship between the I and Q channels, causing portions of one channel to leak into the other one. The quadrature correction algorithm can undo this effect by choosing the matrix coefficients as a function of the amount of quadrature error q present:

$$\left[\begin{array}{c} X \\ Y \end{array}\right] \ = \ \left[\begin{array}{cc} \cos(q/2) & \sin(q/2) & 0 \\ \sin(q/2) & \cos(q/2) & 0 \end{array}\right] \ \left[\begin{array}{c} I(nT) \\ Q(nT) \\ \text{TIME}(nT) \end{array}\right]$$

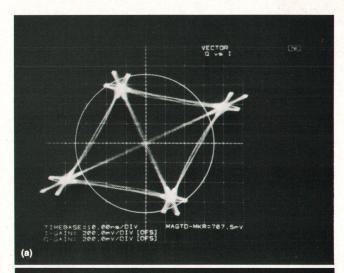

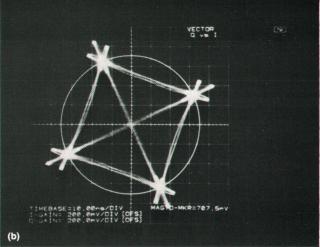

A signal showing both kinds of errors can be corrected by using a matrix that is the product of both these matrices (since matrix multiplication is not commutative in general, it is important to do it in the correct order). The resulting correction matrix becomes a modifier that can operate on any of the original matrices corresponding to the basic display types. This allows the correction to appear in the display versus time as well as the vector display, or any of the other display types available. An example of a QPSK signal before and after errors were removed by the HP 8980A Vector Analyzer is shown in Fig. 11. It is interesting to note that these errors are removed at baseband even though they can be introduced in the system's IF or carrier frequencies.

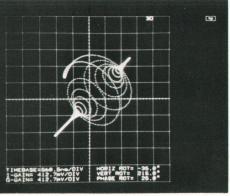

A further extension of the mapping concept results in the 3-D display mode. At any point in time, the I, Q and TIME signals are related to each other in a certain way. The display modes above have focused so far on two-dimensional cross sections of what is in fact a three-dimensional space with the I channel in one axis, the Q channel on another axis, and TIME on the third axis. There are some

cases where being able to capture the three-dimensional essence of these signals adds insight to their true nature. Fig. 12 shows one such display where the same chirp of Figs. 9 and 10 is shown from two arbitrary viewing angles.

**Fig. 11.** (a) QPSK signal corrupted by phase and quadrature errors. (b) After quadrature correction. (c) After quadrature and phase correction.

**Fig. 12.** Three-dimensional rotations of chirp displayed in Figs. 9 and 10.

Features like the phase reversal near the center of the display can be appreciated much more readily now than on the previous pictures. Mathematically, this 3-D display is a simple extension of the 2-D version. In this case, however, all of the matrix coefficients will be nonzero and functions of the three rotation angles selected. As before, the instrument's firmware incorporates quadrature and phase correction effects into the 3-D display by simply multiplying corresponding matrices together.

#### **Triggering**

The HP 8980A is normally used with external triggering when measuring digital radios because the I and Q signals are filtered random data signals. The filtering of the data corrupts the timing for displaying eye patterns or constellations if the I or Q signal is used for triggering. The clock signal from the radio is used as the trigger input to avoid this problem. For other types of measurements, however, the I or Q signals can be used as the trigger source.

The function of the trigger system is to create an ECL-level digital signal with a precise time relationship to the selected trigger input. Basically, the signal is an ECL pulse train at the trigger frequency. This signal starts the timing generation circuit whenever the timing system is ready to take another sample. The trigger system selects the trigger source and sets the trigger level based on the requested value and the attenuation in front of the trigger output of the input amplifier. It uses fast voltage comparators and

sets the trigger thresholds with digital-to-analog converters (DACs). Either dc or ac coupling is available in internal triggering, independent of what is selected for the display.

External triggering is always dc-coupled. Preset levels for TTL and ECL are available in external trigger, as well as variable levels with 40-mV resolution. The most-oftenused trigger threshold setting is **AUTO**, which continuously adjusts the trigger to halfway between the positive and negative peaks of the external input signal. This usually works well for all but the slowest trigger inputs. Another function of the trigger system is to select either ground or ECL terminations ( $50\Omega$  to -2V).

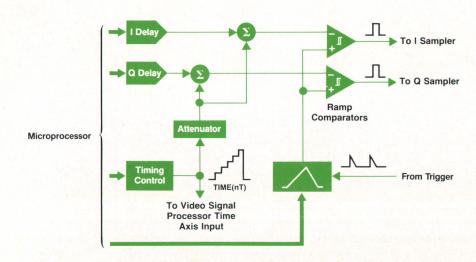

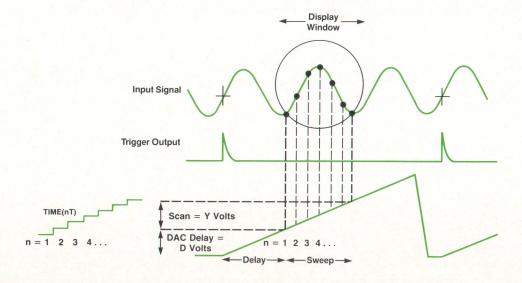

#### **Timing**

The HP 8980A uses a modification of the sequential repetitive sampling technique. In sequential sampling a single sample is taken as a result of a trigger event. By slightly incrementing the delay from trigger every time a new sample is taken, the original waveform can be reconstructed as long as it is repetitive (and stationary). The timing control block of the system's overall block diagram (Fig. 4) generates the sweep control voltage TIME. When the timing generation block receives a trigger, it starts a ramp which is then compared to the TIME voltage. When these two values become equal, a sample pulse is generated and sent to the samplers. The video signal processor uses the TIME signal to position the samples correctly in the display using the fact that this voltage represents time-axis informa-

**Fig. 13.** Timing system block diagram.

tion of the sample in hand.

To accomplish some of the delayed sweep functions of the instrument, the TIME signal is first attenuated and then a dc offset is added to it before it is sent to the ramp comparators (see Fig. 13). The dc offset becomes a time delay after going through the ramp comparator. Since the ramp is designed to span a constant range of voltages, the control signal must be attenuated if a dc offset is added. The instrument's processor, armed with information on what sweep and how much delay is required, decides how much dc offset it needs to add as well as the attenuation factor and the ramp slope (the slope of the ramp can be continuously adjusted with 10 bits of resolution over six decades, starting at 10 ns/V). Fig. 14 shows a timing diagram of the system in which seven subsequent ramps have been superimposed to depict the reconstruction process.

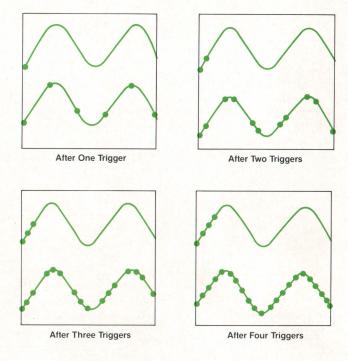

Traditional sequential sampling has the drawback that since only one sample is taken per trigger event, as trigger rates get slower the number of samples taken per second (sample throughput) is reduced significantly. This effect is intolerable in the HP 8980A, which requires a high sample throughput to achieve the display quality needed. To get around this problem the user can enable the HP 8980A's multisample mode.

In the multisample mode the first point on the block is taken at the same time as it would have been during regular sequential sampling. In this case, however, the timing circuit reuses the same timing ramp to generate a sequence of sampling pulses spaced 1.5  $\mu$ s apart until the display window is filled. If the instrument setting is such that the timing ramp is long compared to 1.5  $\mu$ s, a lot of samples can be taken every time a ramp is launched by a trigger event. Contrasting this with the single-sample-per-trigger case found in normal sequential sampling, one can easily see the improvements in data throughput. Now instead of taking one sample per trigger, the timing system takes a block of samples each time a trigger event is received (the size of the block will depend on the instrument setting). Subsequent blocks are shifted in time by one resolution interval from the previous block until the waveform is completely reconstructed. Fig. 15 illustrates this process.

The multisample feature allows the HP 8980A to main-

**Fig. 15.** Signal reconstruction using multisampling. The increased data throughput of multisample mode (bottom trace in each block) is contrasted with normal sequential sampling (upper traces).

tain over a wide range of conditions the fastest sample throughput allowed by the bandwidth of the display unit. Throughput limitations still occur for certain combinations of slow trigger rates and small time windows, such as would be needed to look at low-duty-cycle pulse trains.

To meet the instrument's timing specifications, all of the control voltages used in the timing circuits need to be generated very accurately and the ramp slope precisely known. Calibration plays a major role to ensure that this happens over the six-decade range of specified performance as well as over environmental conditions. The calibration section in the firmware article on page 17 describes in more detail how this is accomplished.

**Fig. 14.** Signal reconstruction using sequential sampling. The events following seven consecutive trigger pulses (n=1 to 7) are superimposed in a single picture. This highlights the relationships between the voltage scanned by the TIME signal and the sweep as well as the relationship between the I (or Q) DAC delay voltage and the I (or Q) delay.

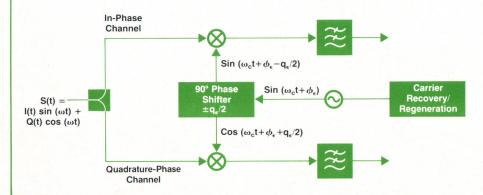

#### Quadrature and Phase Errors in Vector Demodulation

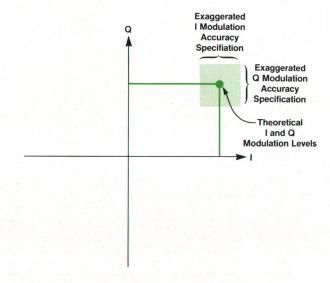

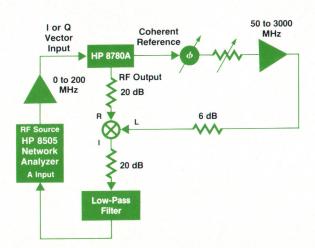

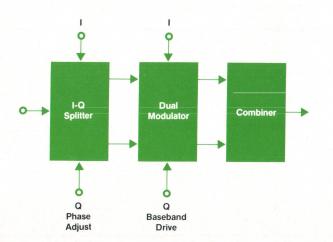

Any practical implementation of vector modulation techniques invariably results in the appearance of phase and quadrature errors. To understand their causes, let's examine the block diagram of a nonideal vector demodulator such as the one shown in Fig. 1.

The RF signal splits into the in-phase (I) and the quadrature phase (Q) paths. The in-phase path is demodulated with a signal that ideally has the same frequency and phase as the carrier. In digital communications systems this unmodulated carrier is in most cases not available to the receiver because the transmitter and receiver are in different physical locations. Therefore, the demodulator must be able to reconstruct the unmodulated carrier from the modulated carrier. This is accomplished in carrier recovery and regeneration circuits, which lock onto the frequency of the modulated carrier but have a difficult time extracting the phase information accurately.

Another major use of vector modulation techniques is found in radar systems. Here the transmitter and receiver share the same physical location (e.g., the nose of an airplane or a mast of a ship). Therefore, the unmodulated carrier reference is available to the receiver for use in the demodulation process. In this case, differences in path lengths to the mixers between the input signal and the oscillator contribute to the phase error term.

The quadrature phase path is demodulated with the same regenerated carrier as the in-phase path, but it is shifted by 90 degrees, resulting in a cosine term. The argument has the same phase error value as the in-phase channel, but the quadrature term has the opposite sign. This quadrature figure describes

inaccuracies in the 90-degree phase shifter. The quadrature error is split equally between the I and Q channels to simplify calculations. What is important to remember is that the in-phase error represents the difference between the modulated carrier and the recovered one while the quadrature error represents deviations from the 90-degree relationship between the drive to the I-channel mixer and the drive to the Q-channel mixer.

The results of these errors are shown mathematically in the following equations describing the demodulated I and Q signals:

$$I'(t) = I(t)\cos(\phi_{\epsilon} - q_{\epsilon}/2) + Q(t)\sin(\phi_{\epsilon} - q_{\epsilon}/2)$$

$$Q'(t) = Q(t)\cos(\phi_{\epsilon} + q_{\epsilon}/2) - I(t)\sin(\phi_{\epsilon} + q_{\epsilon}/2)$$

If no errors are present, I'(t) and Q'(t) are equal to the original I and Q modulations. The presence of phase and quadrature errors introduces leakage between the two channels which in turn deteriorates the performance of the system.

A significant advantage of vector modulation is that it provides two independent channels of information in a bandwidth that a single channel would normally occupy. Sent in quadrature, they can be uniquely recovered at the receiver. To take full advantage of this fact, receivers of this kind strive to minimize the effects of quadrature and phase errors.

Juan Grau

Development Engineer

Stanford Park Division

**Fig. 1.** Vector demodulator block diagram.

#### **ADC** and Measurements

The ADC measures the X and Y signals from the video signal processor to give quantitative voltage measurements. Voltages of I and Q can be displayed at a given time instant by setting the time marker to the desired instant and selecting the **CONTINUOUS I,Q** measurement function. The microprocessor controller sets the timing system for fixed time while it digitizes the X and Y signals. In a vector display, the I and Q voltages are then just the X and Y values, scaled and shifted by the gain and offset settings.

In a similar way, data can be acquired for HP-IB measurements in blocks of up to 1024 pairs. Measurements can be made at a fixed time or across an entire time sweep. I or Q can be measured separately, or together in pairs. Since the measurements are made at the X and Y outputs of the

video signal processor, any phase or quadrature corrections are included before digitizing. These corrections could be done in software in the HP-IB controller that receives the data, but this would take valuable processing time. Making the corrections in hardware is much faster.

Although not designed to be a high-performance digitizing instrument, the HP 8980A's analog-to-digital resolution is higher than many instruments in its bandwidth range. The ADC has 12-bit resolution, but since amplifier noise is about four counts rms, the effective resolution for a single measurement is about nine bits. Most instruments in the 300-MHz-to-1-GHz range have seven or less effective bits because of noise. Finer resolution is possible for repetitive waveforms (i.e., not random data) by calculating the average of a number of measurements in the HP-IB controller.

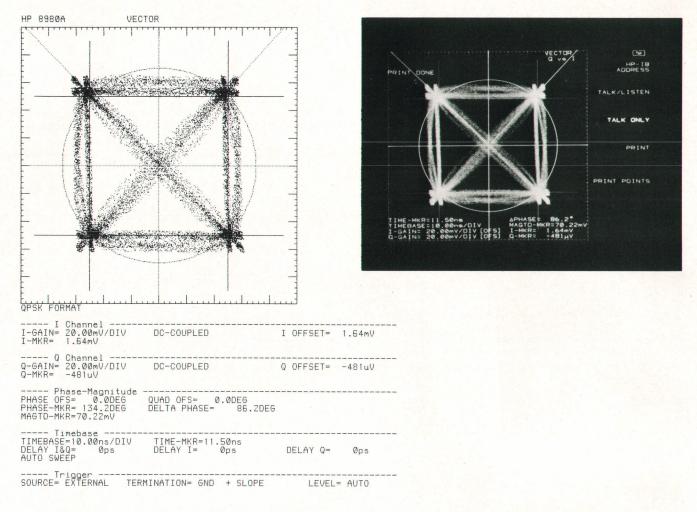

Fig. 16. Printed copy and photograph of corresponding display for QPSK vector analysis.

The digitizing rate is dependent on the timing setup and other factors, but can be as high as 3000 sample pairs per second for fixed time measurements. This is quite slow compared to instruments like waveform recorders and digitizing oscilloscopes, but the time resolution is excellent, down to 50 ps or less. In addition, the HP 8980A digitizes at a fixed delay time relative to the trigger event, which can be an advantage in many situations over the random repetitive digitizing technique used in digitizing oscilloscopes.

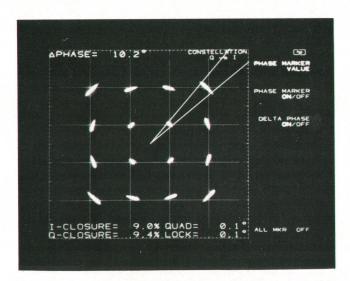

The ADC also collects data for constellation analysis measurements, such as those made by the HP 3709A Constellation Display.<sup>2,3</sup> This function computes the quadrature, lock angle, and closure in I and Q for digital modulation signals. It is a quantitative measure of the radio's performance that can be used to measure a radio carrying live traffic without taking it off-line.

Many users asked for printing or plotting of the screen during our market research. Plotting the screen is impractical because of the unconnected nature of a sampled display of random data. It would be very difficult for the instrument to figure out how to connect the dots. Printing is far easier, however, since a raster pattern is an ordered set of dots already. Since the display is analog and the

printed copy is digital, there is a difference between the appearance of the two. Fig. 16 compares a printed copy with a photo of the display for a complex vector diagram of a QPSK signal.

Finally, the analog-to-digital system is used for servicing the instrument by measuring voltages at various points throughout the instrument. Power supplies and crucial signal lines are measured as part of the self-test and diagnostic procedures. Some of these signals are also needed for performing the extensive self-calibration function, which assures specified accuracy in displayed voltages, timing, and triggering. This calibration is discussed in the following article.

#### **Acknowledgments**

Many others contributed to the hardware design of the HP 8980A Vector Analyzer. Kyle Karnosh designed the CRT display interface and the power supply circuits. Brian Messenger and Paul Lingane designed the trigger and input systems. Stan Little worked on the timing generation circuits, and John Hasen helped by getting our test systems in shape. Product design was by Charles Cook, Barry Rose, and Trevor Burward-Hoy. Ramani Pichumani designed the digital control system. Cindy Jensen worked on various

circuits and helped manage the introduction, along with production engineer Hilda Fong. Our circuit design gurus, Russ Riley and Tim Carey, contributed in many areas to make everything work right together.

#### References

1. K. Hasebe, W.R. Mason, and T.J. Zamborelli, "A Fast, Compact

High-Quality Digital Display for Instrumentation Applications," Hewlett-Packard Journal, Vol. 33, no. 1, January 1982.

2. D.J. Haworth, J.R. Pottinger, and M.J. McKissock, "Dedicated Display Monitors Digital Radio Patterns," *Hewlett-Packard Journal*, Vol. 38, no. 7, July 1987.

3. M.J. McKissock, "Constellation Measurement: A Tool for Evaluating Digital Radio," ibid.

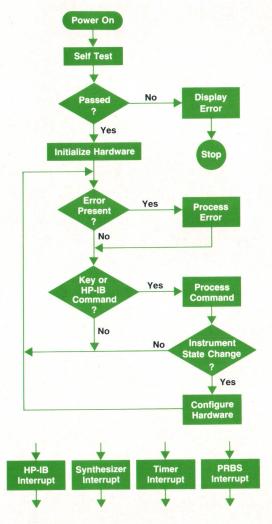

## Firmware System Design for a Vector Analyzer

by Brian S. Messenger, Peter H. Fisher, and Stanley P. Woods

HE TREND IN THE DESIGN of electronic test instrumentation has been to provide the user with greater feature sets and performance while maintaining a consistent and easy-to-use human interface. This has resulted in the need for new methods to allow the user to exercise capabilities both on a lab bench and in an automatic test system environment. The advent of smaller and faster microprocessor systems that can be used in instrument design has opened a new realm of instrument control and calibration possibilities. It has also become possible to add calculation-intensive statistical capability to standalone instruments to allow them to perform functions that would previously have required an additional computer system. The common linkage between all of these advances is the need for writing and integrating large firmware modules for electronic instrumentation.

The HP 8980A Vector Analyzer is an example of this substantial change in the importance of software in electronic instrumentation. In the late 1970s, typical instruments used finite state machines or 8-bit microprocessors and perhaps 1K to 2K bytes of internal firmware. The HP 8980A uses a 32-bit 68000 microprocessor for overall control, in addition to a keyboard processor, an HP-IB (IEEE 488/IEC 625) interface processor, and a CRT display processor. A half megabyte of software is used by the HP 8980A. This software is written in C and, where optimization for speed was critical, in assembly language. In all, the software development task for the HP 8980A required approximately 90 engineer months of development.

The software task for the HP 8980A can be broken into five major blocks. The display software involves controlling grids, softkey menus, and measurement markers on the HP 1345A Display. The interactive help function gives the user information about all instrument functions with fingertip control. The hardware control software is responsible for setting up the state of approximately 250 bits that control everything from switches and digital-to-analog converters (DACs) to measurements and display modes. The

internal calibration software for the HP 8980A allows the instrument's dc accuracy, triggering, and timing circuits to be calibrated with a single keystroke at any time. Finally, for the benefit of automatic test system users, the latest IEEE 488.2 standard is provided for HP-IB measurements and control.

#### **Visual Markers**

The HP 8980A provides the user with a variety of visual markers for quantitative visual measurements on the CRT. All markers have four core functions which perform consistently across all marker menus:

- 1. MKR VALUE, which is used to change marker value and invokes the marker on function below.

- 2. MARKER ON/OFF, which activates and deactivates a marker. This toggle function also invokes the marker value entry function above when the marker on function is

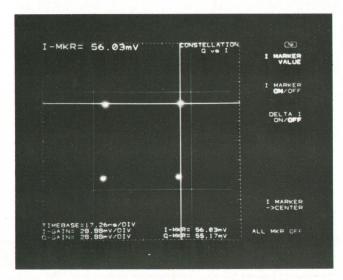

**Fig. 1.** Using the HP 8980A's I and Q markers to determine the I and Q voltage components of one state of a QPSK signal.

selected.

- 3. DELTA MARKER ON/OFF toggle function.

- 4. ALL MKR OFF, which turns all active markers off. An additional function, MKR CENTER, appears on the menu for three types of markers (the I, Q, and TIME markers).

To measure either the I or Q voltage components of a signal visually, the instrument features a pair of I and Q markers. These markers are implemented as straight lines across the grid indicating the voltage at their position relative to the voltage represented at the center of the screen. Fig. 1 shows an example of how the I and Q markers are used to determine the I and Q voltage components of one state of a QPSK signal.

Because the center position of the CRT represents the user offset voltages (offsets dialed in from the front panel), the I or Q marker center function can be used to indicate the offset voltages. This function moves the markers to the CRT center position and displays the marker voltage at that position. This is particularly useful because only an offset annunciator is shown if the offsets are not zero. The actual offset value is not displayed unless the user selects the offset function in the gain and offset menu.

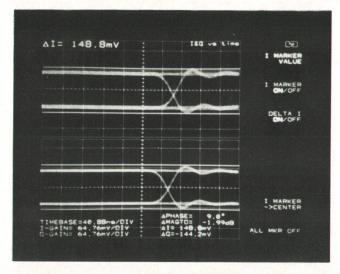

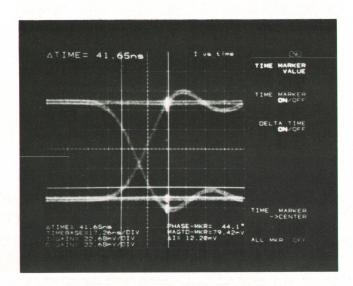

To invoke the I or Q delta marker function, the user first must position the I (Q) marker and then press the DELTA MARKER ON softkey to anchor a marker line at the current I (Q) marker position. The marker readout changes to delta marker values, which represent the voltage difference between the anchored marker line and the current I (Q) marker. Fig. 2 shows an example of how both I and Q delta marker functions are used in an amplitude measurement of the I and Q components of a QPSK modulated signal displayed in the time domain in split-screen display mode.

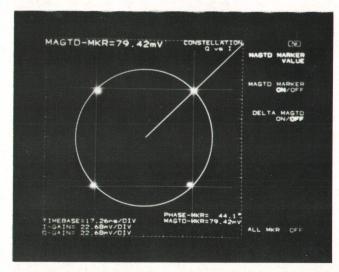

Because of the instrument's special ability to display the phase and amplitude of a signal at the same time, we developed two new marker types to simplify visual measurements of phase and amplitude in the I,Q plane: magnitude markers and phase markers.

The first new marker type, a pair of circular magnitude markers, indicates the magnitude of the vector sum of the

**Fig. 2.** Using the I and Q delta marker functions to measure the amplitude of a QPSK signal displayed in the time domain in split-screen display mode.

I and Q signal components in volts. The magnitude markers are visible only in vector display modes (not time-domain display modes). Fig. 3 shows an example of a magnitude and phase measurement of one state of a QPSK modulated signal. The marker circle maximum extends to the four corners of the grid. The maximum display range for a given gain setting is equivalent to  $5\times \text{volts/div}\times \sqrt{2}$  (the division units in volts/div refer to the general-purpose  $10\times 10\text{-division grid}$ ). Fig. 3 shows the special QPSK grid; only the tick marks of the grid frame indicate the  $10\times 10\text{-division raster}$ .

The delta marker function associated with the magnitude marker function anchors a circular marker at the current magnitude marker position and the marker readout changes to delta magnitude marker in dB. This dB value represents the voltage difference between the magnitude marker anchor and the current magnitude marker position. Upon invoking the delta magnitude function, the readout starts with a dB value of zero since the anchor marker and magnitude marker are superimposed.

The second new marker type, phase markers, was developed to make visual phase measurements. The phase marker is implemented as a straight line originating from the center of the CRT and extending to the extremities of the grid. The marker moves clockwise or counterclockwise around the display like clock hands. The phase is displayed in degrees, starting with zero degrees at the right-hand part of the horizontal scope grid axis. Fig. 3 shows an example of measuring the phase and magnitude of one of the QPSK states.

Like the other markers, the phase marker has a delta marker associated with it. The user invokes the delta phase marker by first positioning the phase marker and then turning the delta marker function on. This anchors a phase marker line at the current phase marker position and changes the marker value readouts to the degree value measured between the anchored marker and the current phase marker position.

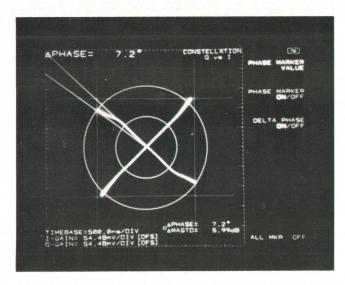

Fig. 4 shows an example of how magnitude and phase

Fig. 3. Measuring the amplitude and phase of a QPSK signal using the HP 8980A's amplitude and phase markers.

**Fig. 4.** Use of amplitude and phase marker functions to determine AM-to-PM conversion and AM-to-AM compression (see text).

markers help in determining amplitude modulation to phase modulation (AM-PM) conversion and amplitude modulation to amplitude modulation (AM-AM) compression. In this example, the HP 8780A Vector Signal Generator is used to generate the QPSK modulated signal. The signal is simultaneously amplitude modulated with a triangular signal using the SCALAR function of the HP 8780A. The output of the HP 8780A is fed into an amplifier/demodulator setup. The demodulated I and Q output signals of this setup are then input into the HP 8980A and displayed in constellation display mode.

The continuous amplitude modulation of the QPSK signal transforms the usual four dots of the QPSK state diagram into four lines forming a cross-like display as shown in Fig. 4.

AM-PM conversion and AM-AM compression occurs because of nonlinearities in the system. In the example illustrated by Fig. 4, these nonlinearities are produced in the amplifier/demodulator setup which introduces PM and amplitude distortion on the measured signal. The phase modulation introduced can be directly seen on the display which shows the signal slightly phase-shifted at the end (ideally there would be a perfectly straight line).

To measure the AM-AM compression, the user sets the HP 8780A output to the level at which the amplifier/demodulator setup shows linear behavior. The user moves the magnitude marker to that position and turns the delta magnitude marker function on. Next, the user increases the output level of the HP 8780A signal appropriately, which in the example shown in Fig. 4 causes AM-PM conversion and AM-AM compression. The user then sets the magnitude marker to the end point of the signal on the CRT. By comparing the output level increase with the delta magnitude reading on the display, the user can easily determine the AM-AM compression.

To measure the AM-PM conversion, the user first moves the phase marker to the linear part of the signal and then turns the delta phase marker function on. In the next step the user moves the phase marker to the end of the signal. In Fig. 4, the delta phase marker reading shows a deviation of 7.2 degrees between the linear portion of the signal and the distorted part, which indicates the AM-PM conversion for the particular level setting.

For time-related visual measurements, the HP 8980A is equipped with a pair of time markers. These markers are implemented as straight vertical lines across the grid on the CRT in all time-domain display modes. In addition, the analog samples on the screen at the time marker instant (value) are intensified. This feature serves two purposes. One is to allow the user to see the time marker position in vector display modes. The other is to indicate the sampling instant while measuring I and Q samples. The instrument measurement functions always measure the signal at the time marker instant. Because the time marker lines show up only in time-domain displays, the intensified samples are the only visual indicator in the vector display modes.

The time marker value is also an important parameter in constellation display mode. Unlike vector display mode, in which samples are taken across the entire time axis, the constellation display mode displays the signal only at the time marker instant.

If I and Q delay is added from the front panel, the time marker value at the left side of the grid is equal to the user I and Q delay. The time marker, like the other markers, has a delta marker function, which is visible only in time-domain-related display modes. The delta time marker function is invoked the same way as the delta I or Q markers. Fig. 5 shows a rise time measurement using the delta time marker function.

#### **On-Line Help Feature**

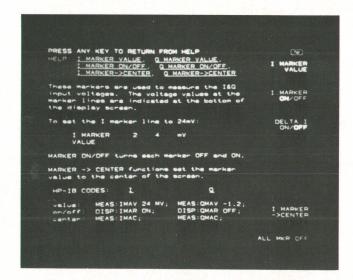

The HP 8980A on-line help feature describes the instrument's front-panel functions. The user invokes the function by pressing the **HELP** key, followed by the front-panel key about which the user wants advice. The instrument responds by writing the help text on the CRT. Along with a description of the key's function, the help feature gives

**Fig. 5.** A rise time measurement using the delta time marker function.

Fig. 6. Help screen for I MARKER VALUE softkey

additional information about any HP-IB mnemonics associated with that key.

To help users avoid feeling lost in the menus when they select a menu softkey, the menu text associated with the softkey is displayed simultaneously with the help text. Fig. 6 shows an example help screen for the I MARKER VALUE softkey.

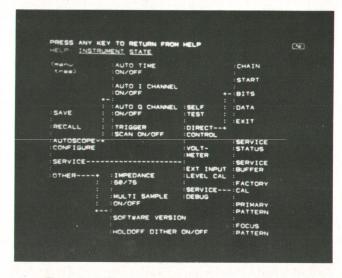

The help text for keys with associated softkey menus is structured in the form of menu trees. These trees visually represent the menu displayed by the softkey plus all lower-level menus under it. This allows the user to scan all softkeys in the instrument without paging through all menus to find a particular function. We found this menu "road map" especially helpful to users searching for less frequently used functions located multiple levels deep in the menu structure. Fig. 7 shows the menu tree invoked by the INSTrument STAte key, the most complex tree in the instrument.

Originally the help text occupied approximately 40K bytes of storage. Because of its size, we decided to reuse some of the text from other help screens and compress the text using the Huffman compression algorithm, resulting in about a 37% space reduction. We decided to use this algorithm because it is easy to implement and because the programs for compression and decompression are so general that they can easily be used in other instruments for similar applications.

In the compression process, the text compression routine generates one dictionary for the entire help text. In the next step, Huffman codes are generated for each paragraph and stored in individual blocks of memory (a paragraph corresponds to one help text screen for a particular key.)

#### Calibration

The HP 8980A calibration involves measurement and modeling of all major aspects of the instrument operation. For simplicity, it can be broken down into three sections: dc voltage calibration, triggering calibration, and timing calibration. Over 350 calibration factors are used in setting up the instrument for the entire spectrum of user-selected

possibilities. These calibration factors may be results of direct measurements such as digital-to-analog converter (DAC) settings that produced a desired result, or they may be calculated using a measurement value and previous calibration factors.

During the initial development of the HP 8980A, two fundamental goals shaped the calibration development. The first goal was to eliminate potentiometers wherever possible. This reduces costly adjustments and allows tighter specifications since temperature drifts can be accounted for by calibrating at the operating temperature. The second goal was to take full advantage of the high-resolution DACs available to provide better accuracy and resolution for the user. This requires more elaborate calibration algorithms, averaging to reduce noise where needed, and verification to guarantee that the calibration results are accurate.

Display Setup. A wide variety of display modes are allowed by the HP 8980A, and the internal dc voltage calibration is intricately tied to their functionality. Considering the three variables I, Q, and TIME, the basic display modes of I versus TIME, Q versus TIME, vector, and constellation all involve displaying one variable along the X axis and one variable along the Y axis. The I and Q versus TIME, vector align, and constellation align display modes all involve swapping back and forth between two basic displays on a time division basis. Finally, the three-dimensional display mode allows the user total flexibility for viewing standard diagrams rotated in any direction. This display mode requires that any combination of I, Q, or TIME can be displayed along the X and Y axes.

Setting up any of the basic display modes is a simplified case of the three-dimensional case. In terms of instrument setup, the X direction and Y direction on the display are described as sums of weighted I, Q, and TIME values:

$$X \text{ Rotated} = W_{IX}I + W_{OX}Q + W_{TIME-X}TIME$$

(1a)

Y Rotated =

$$W_{IY}I + W_{OY}Q + W_{TIME-Y}TIME$$

(1b)

X Rotated and Y Rotated are the names of the analog signals

Fig. 7. Menu tree invoked by INST STA (instrument state) key.

that are switched in to drive the CRT deflection amplifiers directly. In the case of a vector diagram, I is displayed along the X axis while Q is displayed along the Y axis, resulting in  $W_{\rm IX}$  and  $W_{\rm QY}$  weights equal to 1.0 and the remaining weights equal to 0.0. In addition to three-dimensional rotation, the features of phase adjust and quadrature adjust are also implemented by adjusting these weight terms based on the angles desired. All of the weight terms translate directly to coefficients for analog multipliers in the instrument. The purpose of the dc voltage calibration is to determine how to set up switched attenuators, analog multipliers, offset controls, and position adjusts to produce any general-purpose display mode.

DC Voltage Calibration. The dc voltage calibration can be broken down into two successive sections: the RF gain path and the video gain and three-dimensional rotation circuit path. All of the voltage calibration is performed using a precision 0.0V or 0.5V voltage source with an accurate  $50.0\Omega$  source resistance. This calibration signal is switched into the instrument's effective input in place of the user's I or Q channel signal. Calibration of the RF gain path consists of measuring and calculating the relative gains for the range of possible switched attenuator combinations (Fig. 8). This involves switching the 0.0V and 0.5V sources into both channels for the attenuator combinations that will not overrange the input amplifier, and measuring the I-VIDEO and Q-VIDEO signals that are tapped off following the samplers. Up to 1000 analog-to-digital converter (ADC) readings are averaged for the cases where the signal amplitude differences are small and any residual noise is significant. By making four switched attenuator range measurements, it is possible to calculate the relative gains of the remaining three ranges accurately.

The three-dimensional rotation circuits and the position circuits require the greatest number of instrument calibration factors. The first task is to align the CRT digital grid and text information to the analog information in the form of the X Rotated and Y Rotated signals. This is done by writing successive dots at the two diagonal corners of the CRT display grid and measuring the values of the voltages driving the CRT deflection amplifiers. Once these opposite corner voltages are known, the voltages that correspond to any point on the display grid can be calculated. The subsequent calibration is used to determine how to set up various DACs in the instrument so that X Rotated and Y Rotated will produce proper voltages at the CRT deflection amplifiers to line up the user's signals with the CRT grid.

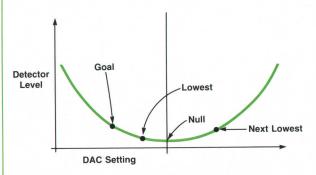

The multipliers used to implement equation set 1 each require three calibration factors for proper setup. The first factor is the null for the signal line. This is defined as the value of the offset DAC that produces an effective input of zero to the signal terminal of the multiplier (Fig. 9). This value is measured by varying the multiplier coefficient with a square-wave input while adjusting the offset DAC until the output of the multiplier remains constant. The value of the offset DAC is the null calibration factor for the specific attenuator range and input coupling. To handle offsets in the RF path accurately, the instrument calibration measures the signal line null for both input couplings with all seven switched attenuator possibilities.

The second multiplier factor is the coefficient null. This factor is measured by using the offset DAC to generate a square-wave input to the multiplier while adjusting the multiplier coefficient until the output of the multiplier remains constant. Finally, the multiplier gain is calibrated by using the 0.5V calibration voltage and adjusting the multiplier coefficient DAC until the proper deflection on the screen is obtained. This result is used to relate the multiplier coefficient to a specific user volts/division setting on a given range. Using the RF gain calibration factor ratios, this one reading can be used to set the volts per division across all attenuator ranges accurately.

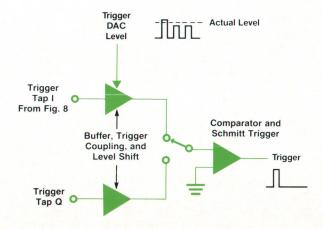

Trigger Calibration. The internal trigger calibration for the HP 8980A is necessary to calibrate the gains and offsets in the trigger signal path. The internal trigger signals are produced by tapping the input signals, buffering and level shifting them, selecting the proper channel, and then driving a high-frequency trigger level comparator and Schmitt trigger (Fig. 10). The instrument allows the user to set up various conditions of input coupling, trigger coupling, switched attenuator settings, trigger slope, and internal trigger level.

A sequence of only eight different conditions must be measured per channel to model all of the possible user internal trigger setups accurately. During calibration, the instrument input is held at a precise 0V or 0.5V level. The trigger DAC which is used to set the variable trigger level can be stepped to create an artificial square-wave input to the trigger level comparator. The trigger level comparator may or may not generate a trigger signal that will initiate a timing ramp. Using a special setup, a single-shot trigger event can be detected in the timing system of the instrument. For each of the trigger calibration factor setups, a binary search algorithm is used to determine the trigger

Fig. 8. Calibration of RF gain path requires measuring the relative gains for the various possible switched attenuator combinations.

DAC value that corresponds to the dc input voltage used. To test each value in the binary search, the trigger DAC is reset to one extreme or the other based on the trigger slope that is being calibrated. This allows a new positive-going trigger edge to be generated if the trigger DAC level is stepped across the input voltage level. When a trigger DAC calibration factor is determined, it is checked to guarantee that it is accurate and not a result of a stuck bit affecting the binary search.

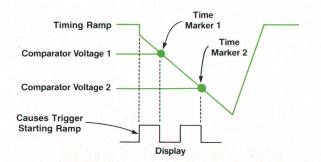

Timing Calibration. The timing system of the HP 8980A requires calibration of the timing sweep and of the various possible delays. Accurately setting up the timing sweep requires that the slope of the timing ramp be known in volts/second. This value is measured for specific setups on each of the six timing ramps. Internal to the instrument, a variable-frequency, crystal-based timing signal is generated and can be switched into the I and Q inputs. This signal covers a range of 100 Hz to 16 MHz, which allows two cycles of the calibration timing signal to be displayed for each ramp range under test. The fine adjustment of the ramp slope is used on each ramp range to bring the first and second falling edges of the positive-edge-triggered square wave to positions at 25 and 75 percent of full screen.

The timing sweep calibration requires that sharp edges with virtually no timing jitter be analyzed to determine their position on the screen. The instrument's time marker has an internal resolution of 10 bits, which translates to 1024 distinct settings across the display screen. The timing sweep calibration uses steps of 100 time marker counts to window in on the falling edges under test. It then steps 10 counts at a time to fall in close proximity to the edge. Finally it is moved along one count at a time until the edge is crossed. When single-count steps are used, 25 measurements of the signal are averaged to reduce any error caused by jitter on the calibration signal. This averaging allows an accurate determination of the closest time marker value to the actual threshold. This can result in a half count of time marker accuracy in this measurement.

The time marker values corresponding to two adjacent falling edges of the calibrated timing signal are determined (Fig. 11). The time marker is frozen at each of these edges, and the ramp comparator voltages for these two points are measured. The ramp comparator voltage difference and the precise period of the input signal in seconds are then used to calculate the ramp slope in seconds/volt. Knowing the six different ramp slopes from calibration, the time base can be set up accurately from 500 ps/div to 2 ms/div.

#### **Display Refresh Control**

The HP 8980A uses a modified high-resolution HP 1345A

Fig. 9. Multiplier setup for measuring gain of circuit in Fig. 8.

Display. The modifications allow the HP 1345A Digital Display information to be brought out of the display and multiplexed with the analog X Rotation and Y Rotation signals at the output of the three-dimensional rotation circuitry. This multiplexed signal is then used to drive the CRT deflection amplifiers directly. The major advantage of this method compared with using a purely digital display is the significantly faster rate that sampled points can be written to the screen. The HP 1345A Display requires a SYNC pulse to produce a rewrite of the digital grid and text that is stored in CRT memory. Generally, about 20 percent of the time is spent writing the digital grid and text information at a rate sufficient to avoid flickering. This leaves approximately 80 percent of the time for switching to displaying the user's analog input signals.

The challenge in using a system such as this is that synchronization could occur between the user trigger signal and the digital signal refresh. As an example, if this system used a fixed 60-Hz digital refresh rate and the user analyzed a signal with a 60-Hz trigger rate, it could be possible that the user's signal would not be seen. The I and Q versus TIME display mode will also run into difficulties if a fixed refresh rate is used. In this case, sections out of the alternating sweeps might be missed at lower trigger rates. These considerations resulted in the need for an adaptive system to handle digital refresh and alternating sweeps in the I and Q mode.

The inputs to the system are a pulse from an internal 120-Hz timer, an end-of-timing ramp pulse, and an end-of-timing sweep pulse. At low sweep and trigger rates, it is necessary to monitor the end-of-timing ramp pulse to avoid starting a slow timing ramp and then interrupting it before sampling and displaying a point. The end-of-sweep pulse is used to guarantee that the same number of traces are drawn for each channel in the I and Q alternating display mode. This avoids problems where one channel would be brighter, then dimmer, then brighter, etc. The end-of-sweep pulse is also used to guarantee that switchovers are done after a sweep is complete.

The 120-Hz timer is used to guarantee that the digital information will always be displayed after various timeouts based on the user's sweep mode selection. When users are in the AUTO SWEEP or FREE RUN modes, the system will

Fig. 10. Internal trigger generation circuitry.

automatically generate a trigger signal if the trigger rate is too low. This simplifies the digital refresh and alternate functions since predictable timing sweeps are generated and can be interrupted at specific times to display the digital information. In the TRIGGERED SWEEP mode, the signal integrity on screen is maintained down to a trigger rate of less than 5 Hz. For this reason, the digital information is allowed to flicker to allow clean viewing of the user's signal in the TRIGGERED SWEEP mode. At trigger rates below 5 Hz, the signal may appear broken up, but it can still be measured.

#### **HP-IB Firmware**

The HP 8980A's HP-IB firmware consists of three separate blocks of code:

- HP-IB driver

- Interface routines

- Command routines.

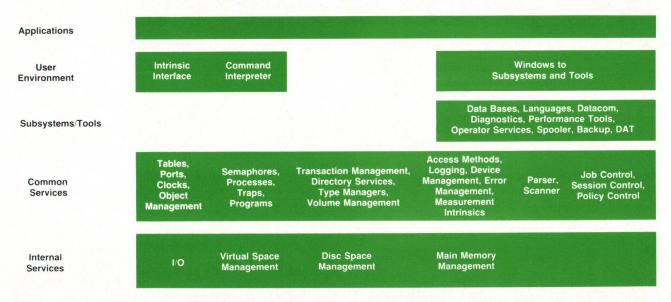

The first block is written in 68000 assembly language and handles the major portion of the IEEE 488.2 standard implementation. In addition, it handles many of the IEEE 488.2 common commands. This powerful module is reusable.