# HEWLETT-PACKARD

**NOVEMBER 1986**

# HEWLETT-PACKARD JOURNAL

November 1986 Volume 37 ● Number 11

#### **Articles**

4 Molecular-Scale Engineering of Compound Semiconductor Materials, by Douglas M. Collins The use of molecular-beam epitaxy allows control of composition and doping on an atomic scale.

- 6 Compound Semiconductor Alloys and Heterojunctions

- 8 The Modulation-Doped Heterojunction

10 Extending Millimeter-Wave Diode Operation to 110 GHz, by Eric R. Ehlers, Sigurd W. Johnsen, and Douglas A. Gray Developing more rugged, integratable diode structures is the key.

13 26.5-to-40-GHz Waveguide Detector

1 4 Diode Integrated Circuits for Millimeter-Wave Applications, by Mark P. Zurakowski, Domingo A. Figueredo, Scott S. Elliott, George A. Patterson, William J. Anklam, and Susan R. Sloan These tiny GaAs ICs operate to above 100 GHz for frequency translating and nonlinear signal processing.

22 Unbiased Subharmonic Mixers for Millimeter-Wave Spectrum Analysis, by Robert J. Matreci These units let you use your microwave spectrum analyzer for measurements up to 110 GHz.

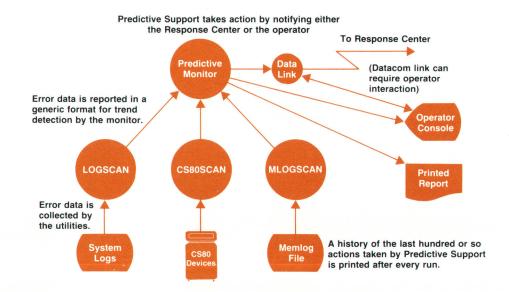

30 Predictive Support: Anticipating Computer Hardware Failures, by David B. Wasmuth and Bruce J. Richards Running on a customer's system, this software collects error data, detects trends, and warns of possible failures.

- 32 Systems Design for Worldwide Delivery of Customer Support

- 33 Logging Event Data in the Trend Log

34 AIDA: An Expert Assistant for Dump Readers, by Lynn R. Slater, Jr., Keith A. Harrison, and Craig M. Myles This troubleshooting tool automatically checks for data consistency while providing readers with tools to pursue their own inquiries.

35 What Is a Memory Dump?

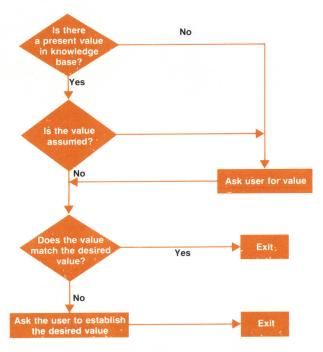

42 A Troubleshooting Aid for Asynchronous Data Communications Links, by Brian T. Button, R. Michael Young, and Diane M. Ahart This expert system guides troubleshooters through the solution of datacom link problems.

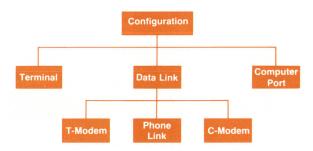

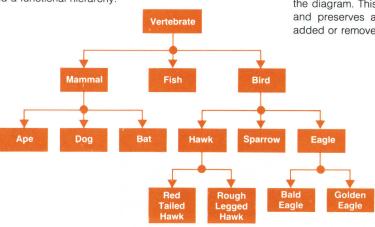

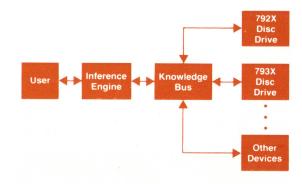

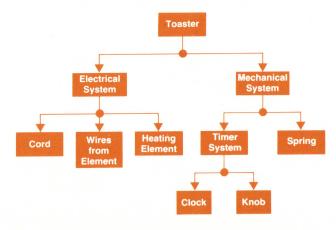

46 Hierarchies

48 A Rule-Based System to Diagnose Malfunctioning Computer Peripherals, by George R. Gottschalk and Roy M. Vandoorn A peripheral independent inference engine, a separate knowledge base, and representations of various peripherals characterize this expert system.

Multilevel Constraint Based Configuration, by Robert I. Marcus Multilevel constraints provide an alternative or supplement to forward chaining.

#### **Departments**

- 3 In this Issue

- 3 What's Ahead

- 27 Authors

#### In this Issue

When engineers talk about millimeter waves, they're referring to electromagnetic energy in the frequency range of 26 to 300 gigahertz, more or less. Although this region of the electromagnetic spectrum is beginning to be used for high-speed communications, high-resolution radar, guidance systems, and radio astronomy, circuit elements such as transistors are available only for the low end of this frequency range, and integrated circuits are hard to come by. In the last few years, Hewlett-Packard Laboratories and the HP Microwave Technology Division have achieved notable success in developing small-scale integrated and hybrid circuits that operate at 100

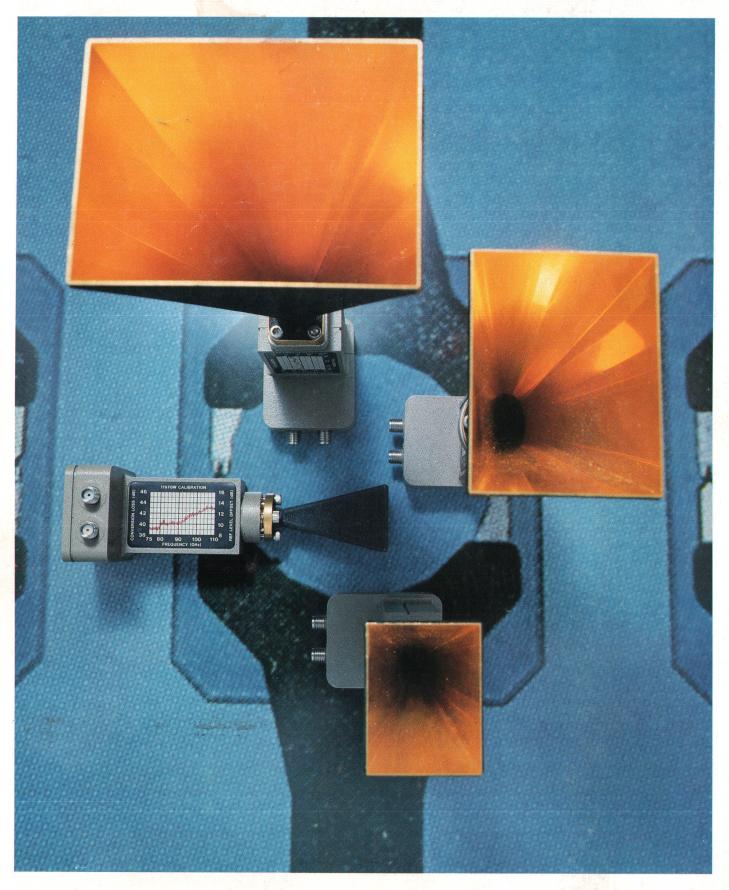

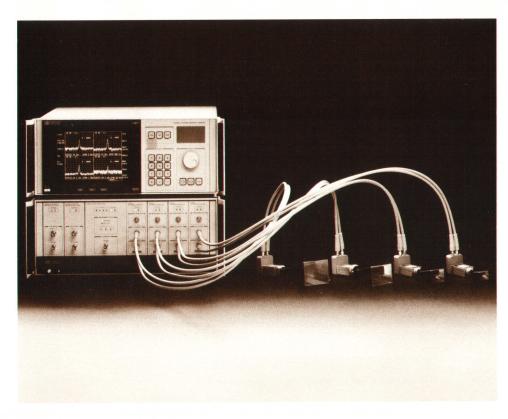

GHz and beyond. Using gallium arsenide and related compounds and a process known as molecular beam epitaxy (MBE), HP engineers have fabricated Schottky and modified barrier diodes, along with ICs and hybrids based on these diodes. Mainly useful for nonlinear and frequency translation applications such as detectors, samplers, multipliers, and mixers, they are now available in several new millimeter-wave products from HP. On page 4, Doug Collins of HP Laboratories tells us how MBE works. Modified barrier diodes and their uses in products are discussed in the article on page 10. Fabrication of ICs and hybrids is the subject of the article on page 14, and the article on page 22 describes a series of mixers that use the new GaAs diodes to extend the range of microwave spectrum analyzers to 110 GHz. The cover photograph shows several of these mixers with their horn antennas of various sizes for operation in different frequency bands.

The remainder of this issue is devoted to several papers on unusual software tools for the support of HP computer systems in the field. These are forward-looking efforts, aiming to predict failures before they happen and to use artificial intelligence (AI) technology in expert systems for troubleshooting and configuring computer systems. Predictive Support (page 30) is a software package that lives on a customer's system, counts soft errors, and notifies HP support personnel when it spots an ominous trend. Reports indicate that it works and customers like it. AIDA (page 34) is an expert system that helps HP support personnel analyze HP 3000 Computer memory dumps. A dump is a last-resort method of finding a computer problem. It may contain many megabytes of information and is hugely complex to analyze. AIDA's major contribution is its formatting capability, which helps the human expert organize all that data. That it can also find corrupt data automatically is considered a bonus by many HP troubleshooters. Schooner and IPT (pages 42 and 48) are expert systems for troubleshooting datacom links and disc drives. respectively. They've proved useful for troubleshooters learning the business and for solving the easier problems, leaving experienced personnel more time to tackle the tougher problems. Mycon (page 54) is a prototype expert configurator for computer systems. Worthy of note is its concept of multilevel constraints, which supplement and refine traditional approaches to the design of expert configurators.

R. P. Dolan

#### What's Ahead

The December issue will be another in our series covering HP Precision Architecture topics. Subjects included are the HP-UX operating system for technical and real-time HP Precision Architecture computers such as the HP 9000 Model 840, and ALLBASE, the data base management system for both technical and commercial HP Precision Architecture computers. December is also our annual index issue.

# Molecular-Scale Engineering of Compound Semiconductor Materials

The ever increasing sophistication of semiconductor electronic devices and integrated circuits continues to place increasing demands on the precision with which the underlying semiconductor materials are produced. The development of molecular beam epitaxy allows the highly repeatable growth of compound semiconductor epitaxial films (such as GaAs and  $Al_xGa_{1-x}As$ ) with atomically abrupt changes in alloy composition and doping and with excellent uniformity.

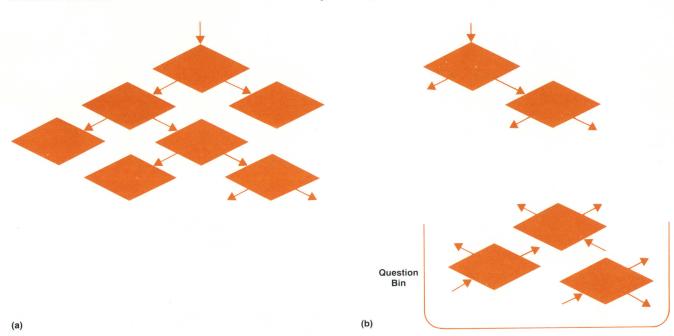

#### by Douglas M. Collins

EMICONDUCTING MATERIALS provide the foundation upon which today's high-technology electronics industry is built. While silicon is the most widely used semiconducting material, and that for which the most advanced technology has been developed, its physical properties are not suitable for many of today's device needs. Thus, the use of other semiconducting materials whose electronic band structure leads to specific properties that make them more suitable than silicon for specific applications is becoming more and more common.

One such class of semiconductors is that known as the group III-V compound semiconductors. This name is derived from the fact that these materials are compounds of elements found in columns III and V of the periodic table. The most common example is gallium arsenide (GaAs),

which is widely used in microwave and optoelectronic devices.

To produce high-quality compound semiconductor materials for high-performance electronic or optoelectronic devices, it is necessary to use epitaxial growth techniques. This is especially true for those devices that require heterojunctions (for a discussion of heterojunctions, see box on page 6). In general, an epitaxial growth process is any process in which chemical elements or compounds are deposited onto a single-crystal substrate under conditions such that the deposited materials become precisely arranged upon the substrate, yielding a single-crystal deposited, or epitaxial layer. In fact, the word epitaxy is derived from the Greek words epi (meaning "on") and taxis (meaning arrangement).

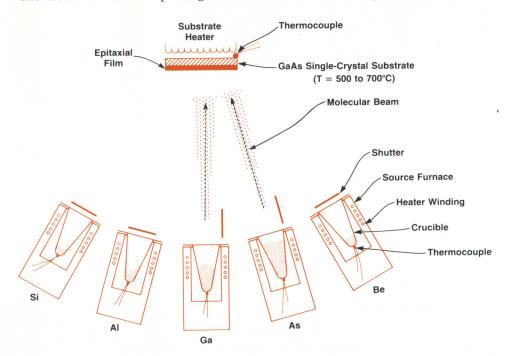

**Fig. 1.** Schematic representation of the molecular beam epitaxy (MBE) technique.

To push devices to higher and higher levels of performance, it is necessary to control the epitaxial growth process precisely. The molecular beam epitaxy technique is one that provides for the precise growth of complex III-V compound semiconductor structures which are particularly well-suited for high-speed (e.g., millimeter-wave) device and integrated circuit applications.

#### The MBE Technique

Molecular beam epitaxy (MBE) can best be described as a highly controlled ultrahigh-vacuum evaporation/deposition process. The apparatus used for the MBE growth of GaAs and  $Al_xGa_{1-x}As$  is shown schematically in Fig. 1. (For a discussion of alloy semiconductors such as  $Al_{\mathbf{x}}Ga_{1-\mathbf{x}}As$ , see box on page 8.) The principal components in this system are the resistance-heated source furnaces. the source furnace shutters, and the heated substrate station. Three of the source furnaces contain the elements Ga. Al, and As which, when reacted on the heated single-crystal substrate, produce the epitaxial semiconductor layer. The other two sources contain silicon and beryllium, the two most commonly used dopants in the MBE growth of GaAs and Al<sub>x</sub>Ga<sub>1-x</sub>As. Silicon substitutes for the gallium or aluminum atoms on the group-III sublattice resulting in one extra electron; hence silicon is an n-type, or donor, impurity in these materials. Beryllium also substitutes for the aluminum or gallium atoms, but with one less electron; hence beryllium is a p-type, or acceptor, impurity in these materials.

The rate of evaporation of the source materials, and thus

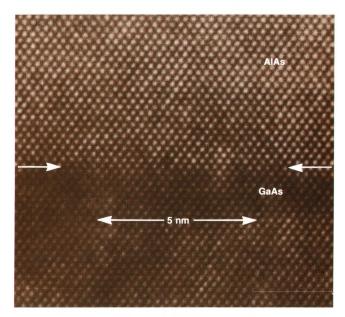

**Fig. 2.** High-resolution transmission electron micrograph of atomically abrupt GaAs/AlAs heterojunction formed by MBE.

the flux of atoms or molecules arriving at the substrate surface, is determined by the temperature of each of the sources. Each source temperature is individually controlled to within  $\pm 0.2$ °C, which results in less than  $\pm 1\%$  variation in the source flux.<sup>1</sup> The temperatures (and thus the fluxes) of gallium and aluminum (both of which evapo-

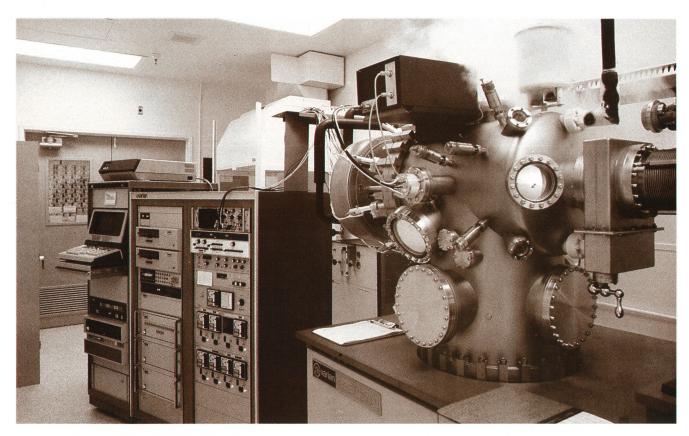

Fig. 3. HP's MBE systems (right) are controlled by HP 1000 Computers (left).

### **Compound Semiconductor Alloys and Heterojunctions**

The properties of semiconducting materials that are of practical interest depend on the material's crystal structure, the interatomic spacing in the crystal, the electronic band structure, and the thermodynamics of defect formation, in particular the incorporation of impurity or dopant atoms that alter the electronic properties in a desired fashion. These factors combine to determine the bandgap energy  $E_g$  of the semiconductor (and whether the bandgap is "direct" or "indirect"), the transport properties of electrons and holes (in particular the mobilities of these charge carriers), and the practical matter of being able to control the electron and hole concentrations over the ranges necessary for use in devices.

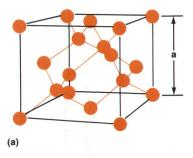

Silicon crystallizes into the so-called "diamond" structure (Fig. 1a), which can be described as two interleaved face-centered cubic lattices (an FCC lattice has an atom at every corner of a cube in addition to an atom at the center of every face of the cube). One FCC lattice has its origin at 0, 0, 0 and the other FCC lattice has its origin at a/4, a/4 (only a portion of the second lattice is shown in Fig. 1). This results in a tetrahedral coordination between each silicon atom and its four nearest neighbors.

Most of the III-V compound semiconductors, including GaAs, crystallize into the so-called "zincblende" structure (Fig. 1b). This structure is remarkably similar to that of silicon. In fact, it is the diamond structure, except that one of the two interleaved FCC sublattices is composed of group-III atoms (e.g., gallium) while the other is composed of group-V atoms (e.g., arsenic). Thus each group-III atom is tetrahedrally bonded to four nearest-neighbor group-V atoms, and each group-V atom is tetrahedrally bonded to four nearest-neighbor group-III atoms.

The additional complexity of the zincblende structure offers a degree of freedom not available in elemental semiconductors such as silicon and germanium. This freedom is the ability to mix different group-III elements on the group-III sublattice as well as different group-V atoms on the group-V sublattice. Thus we can form ternary (e.g., Al<sub>x</sub>Ga<sub>1-x</sub>As) and quaternary (e.g.,  $In_{x}Ga_{1-x}As_{y}P_{1-y})$  alloy semiconductors, where 0  $\leq$  x  $\leq$  1 and  $0 \le y \le 1$ . The subscripts x and y in these chemical formulas indicate the fraction (commonly called the mole fraction) of each sublattice that is occupied by each element. Since, in general, different semiconductors have different bandgap energies and different electron and hole transport properties, the ability to form alloy semiconductors provides the materials scientist with the freedom to engineer the material to the needs of the device physicist. Thus it is possible, for example, to adjust the bandgap of a semiconductor to give the desired wavelength of emission for a light-emitting diode.

In addition to providing the flexibility of engineering semiconductor material properties by forming these alloys, compound semiconductor technology provides an added capability with far-reaching consequences—the ability to join two different semiconductor materials intimately together to form a semiconductor heterojunction. This is conceptually very similar to joining together p-type and n-type silicon to form a semiconductor pn homojunction. However, it leads to many more potential applications of III-V compound semiconductors. For example, if a thin layer (approximately 0.2 micrometer) of one semiconductor is sandwiched between two layers of a second semiconductor that has a larger bandgap and a smaller index of refraction, the center layer will serve to confine both charge and light, thus providing two of the necessary conditions for the formation of a population inversion in this layer, which leads to semiconductor laser action. 1 Such structures are known as double heterojunctions. Another technologically important heterojunction is the modulation-doped heterojunction (see box, page 8), which is important to the very high-speed operation of the modulation-doped field effect transistor (MODFET, also known as the high-electron-mobility transistor, or HEMT).2

To form semiconductor heterojunctions with a high degree of structural perfection, the two semiconductors must have identical (or compatible) crystal structures and nearly equal interatomic spacings, or lattice constants (dimension a in Fig. 1). This requirement can be met by using compound semiconductor alloys that have the same crystal structure while simultaneously choosing alloy compositions (x and/or y in the above chemical formulas) that result in the same lattice constants. This is a condition which is referred to as lattice matching. In the GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As material system discussed in the accompanying article, the lattice match is nearly perfect for all values of x.

#### References

- H.C. Casey and M.B. Panish, Heterostructure Lasers: Part A, Fundamental Principles, and Part B, Materials and Operating Characteristics, Academic Press, New York, 1978.

- 2. H. Morkoç and P.M. Solomon, "The HEMT: A Superfast Transistor," IEEE Spectrum, Vol. 21, no. 2, February 1984, pp. 28-35.

Fig. 1. Semiconductor crystal structures (a = lattice constant). (a) Diamond structure for silicon, carbon, germanium, etc. (b) Zincblende structure for GaAs, GaP, InSb, etc. Bonds between nearest neighboring atoms are shown in color.

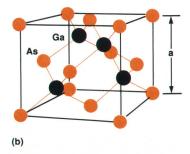

**Fig. 4.** Free electron concentration at room temperature (300K) for Si-doped MBE GaAs as a function of silicon source temperature.

rate as monatomic beams) are chosen to give the desired growth rate and alloy composition. The temperature of the arsenic source (arsenic evaporates as the  $As_4$  molecule) is chosen such that the  $As_4$  flux is slightly higher than that required for growth of stoichiometric GaAs or  $Al_xGa_{1-x}As$  (i.e., where the number of gallium and aluminum atoms incorporated into the film is equal to the number of arsenic atoms incorporated into the film). The small excess of ar-

senic is used to ensure nearly perfect stoichiometry since, at the substrate temperatures used (typically 500 to 700°C), the arsenic will bond only to gallium or aluminum and not to itself. The excess arsenic evaporates from the film surface.<sup>2</sup> Similarly, the temperatures of the silicon and beryllium sources are chosen such that the fluxes of these elements lead to the desired concentrations of n-type and p-type doping, respectively.

The temperatures of the gallium and aluminum sources are typically chosen to result in a growth rate of 1.0  $\mu$ m/hour. This corresponds to only one molecular layer of GaAs or  $Al_xGa_{1-x}As$  per second. Since each source furnace is equipped with its own individual shutter that can be opened or closed in a small fraction of a second, it is a simple matter to control the composition or doping in an epitaxial film on an atomic scale. An example of an atomically abrupt GaAs/AlAs heterojunction (grown by closing the gallium shutter and opening the aluminum shutter simultaneously) is shown in the high-resolution transmission electron micrograph of Fig. 2.

The MBE systems in operation at Hewlett-Packard Company (e.g., see Fig. 3) are interfaced with HP 1000 Computers that control the temperature setpoints for the source furnaces and the substrate, the source shutter operation, and the growth times for all layers in multilayer films. In addition to having the capability for abruptly changing the composition or doping of MBE films, the computer is also used to contour alloy compositions and doping profiles programmably to achieve specific materials structures for use in particularly high-performance devices.<sup>3</sup>

For the high degree of control offered by MBE to be of practical use, it is necessary that the undesirable background impurity levels in MBE films be as low as possible and that the films be highly uniform. These conditions are easily met in the MBE growth of GaAs. The ultrahigh vacuum system used in MBE is pumped by ion and titanium sublimation pumps and includes extensive liquid-nitrogen cryoshrouding to pump condensable gases such as water vapor. Background partial pressures of undesirable gases are typically below  $10^{-11}$  torr. This allows undesirable impurity levels as low as ten parts per billion to be achieved. Continuous rotation of the substrate during growth leads to demonstrated uniformities in thickness (or growth rate) and doping concentration of better than  $\pm 2\%$  across a two-

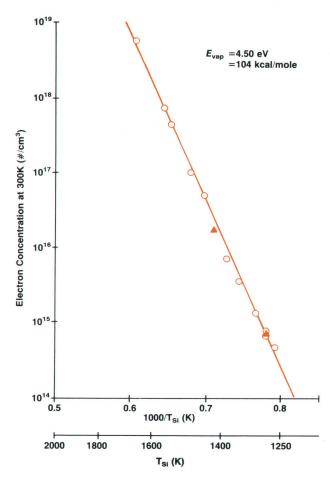

**Fig. 5.** Mobilities for Si-doped MBE GaAs as a function of free electron concentration at 77K.

### The Modulation-Doped Heterojunction

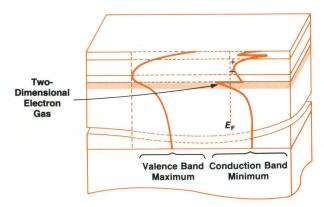

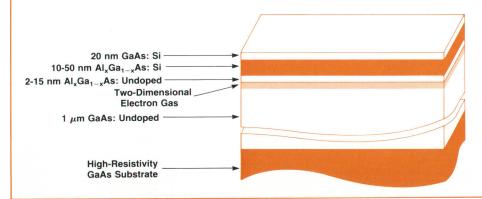

The accompanying article demonstrates that MBE is capable of producing GaAs and Al<sub>x</sub>Ga<sub>1-x</sub>As films with a high degree of control over doping concentration and alloy composition and with extremely abrupt heterojunction interfaces. All of these capabilities are important for the realization of the high-speed device known as the modulation-doped FET. The layered material structure upon which this device is based is commonly referred to as a selectively doped, or modulation-doped heterojunction (see Fig. 1).1 It has been most commonly produced in the GaAs/ Al<sub>x</sub>Ga<sub>1-x</sub>As material system, although other semiconductor heterojunctions have also been used.<sup>2</sup> The epitaxial layer structure is grown on a high-resistivity (107 ohm-cm) GaAs substrate. The first layer is undoped GaAs approximately one micrometer thick, which must be of very high purity (typically less than 1015 ionized impurities per cubic centimeter). The second layer is undoped  $Al_xGa_{1-x}As$  (x = 0.3) which, depending on the desired properties of the structure, will typically be between 2 and 15 nanometers thick. This corresponds to only 8 to 60 atomic layers. The atomic scale abruptness of the heterojunction between these two layers and the precise control of the undoped Al<sub>0.3</sub>Ga<sub>0.7</sub>As "spacer" layer thickness are critical to the proper performance of this device. The third layer is silicon-doped ( $N_{Si} = 2 \times 10^{18}$  $cm^{-3}$ )  $Al_xGa_{1-x}As$  with x typically the same as that in the undoped spacer layer which, again depending on the desired properties of the structure, will be between 10 and 50 nanometers thick. The fourth, and last, layer is n-type GaAs (n =  $2 \times 10^{18}$  cm<sup>-3</sup>) approximately 20 nanometers thick. This layer facilitates making low-resistance ohmic contacts to the structure.

The special properties of this structure that make it of interest for high-speed device applications are best understood by referring to the energy band diagram shown in Fig. 2. Here we see that a conduction band discontinuity is formed at the abrupt GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As interface. This is accompanied by depletion of electrons from the Al<sub>x</sub>Ga<sub>1-x</sub>As and accumulation of these electrons in the GaAs. The potential "notch" in which these electrons reside confines the electrons to a region so thin that they behave as a two-dimensional system. This system is commonly referred to as a two-dimensional electron gas. This electron gas has many similarities to the two-dimensional electron gas in the gate channel of a silicon MOSFET. However, there are two very important differences. First, the GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterojunction is very nearly structurally perfect and thus electrons traveling parallel to this heterojunction interface are unlikely to scatter from structural defects. Second, since the GaAs is of very high purity and the ionized silicon donors in the Al<sub>x</sub>Ga<sub>1-x</sub>As are set back from the heterojunction interface by the spacer layer thickness, scat-

**Fig. 2.** Energy band diagram for structure of Fig. 1. The twodimensional electron gas formed in the structure is ideal for the conducting channel of a FET.

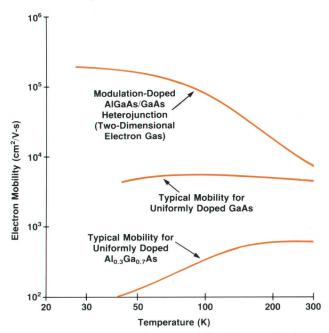

**Fig. 3.** Comparison of electron mobilities for a modulation-doped heterojunction and the two uniformly doped materials used to form the heterojunction.

**Fig. 1.** Cross section of a modulation-doped heterojunction.

tering from the silicon donor atoms is minimized. These two factors result in excellent transport properties for electrons in this modulation-doped heterojunction structure.

The effect on electron transport properties is shown in Fig. 3 where the significantly enhanced mobilities found in these heterojunction structures (top curve) are compared with those observed in uniformly doped GaAs and Al<sub>0.3</sub>Ga<sub>0.7</sub>As with comparable sheet electron concentrations. (In this case,  $n_s = 6 \times 10^{11}$ cm<sup>-2</sup>, which is comparable to the sheet carrier concentration in the channel of an FET). This data shows that the mobility in the modulation-doped structure is a much stronger function of temperature than the mobilities in the uniformly doped films. This occurs because the mobility at higher temperatures in the modulation-doped structure is still dominated by phonon scattering

(i.e., lattice vibrations). However, even at room temperature, the modulation-doped structure exhibits a mobility that is a factor of 1.5 to 2 higher than in the uniformly doped GaAs material. In short-gate-length MODFETs this results in an increase in the electron peak velocity by a factor of 1.5 to 2 and thus a comparable increase in the speed of operation of the device.3

#### References

- 1. R. Dingle, et al, "Electron Mobilities in Modulation-Doped Semiconductor Superlattices," Applied Physics Letters, Vol. 33, 1978, pp. 665-667.

- 2. T.P. Pearsall, et al, "Selectively-Doped AllnAs/GalnAs Heterostructure Field Effect Transistor," IEEE Electron Device Letters, Vol EDL-4, no. 1, 1983, pp. 5-8.

- 3. M. Hueschen, et al, "Pulse Doped MODFETs," 1984 International Electron Devices Meeting Technical Digest, pp. 348-351

inch diameter substrate.

### MBE Grown GaAs and Al<sub>x</sub>Ga<sub>1-x</sub>As

The realization of the precise control of epitaxial film parameters promised above can best be demonstrated by presenting results of doping and alloy composition control for MBE films. Fig. 4 shows the free electron concentration (n, as measured by the Hall effect<sup>4</sup>) at room temperature for Si-doped MBE GaAs as a function of the reciprocal of the silicon source temperature. Several important points may be made from this data. First, it is clear that we have the capability of varying the n-type doping of MBE GaAs over a wide range (from less than 10<sup>15</sup> cm<sup>-3</sup> to 5×10<sup>18</sup> cm<sup>-3</sup>, which corresponds to approximately 0.02 to 100 parts per million) with a high degree of control. In fact, the slope of the precisely exponential variation in n with 1/T<sub>Si</sub> corresponds closely to the activation energy for the evaporation of silicon, indicating that the silicon incorporation rate is directly proportional to the silicon flux. The two different symbols in Fig. 4 correspond to two different

series of MBE growth runs, the second having been carried out after refilling the gallium and arsenic source furnaces. Thus excellent control and repeatability are readily achieved in the MBE growth of GaAs.

To achieve superior performance of electronic devices, it is necessary not only to control carrier concentration precisely, but also to assure good carrier transport properties. A common measure of the quality of n-type GaAs is the electron mobility. Mobility, as the term suggests, is a measure of the ease with which the charge carriers move through the crystal lattice. In particular, high mobilities in lightly doped n-type GaAs at low temperatures (e.g., liquidnitrogen temperature of 77K) are indicative of low concentrations of background impurities since, under these conditions, the mobility is dominated by scattering of electrons by impurities in the crystal. Mobilities for Si-doped, MBEgrown GaAs are shown in Fig. 5 as a function of the free electron concentration. This data was obtained at a temperature of 77K, where impurity scattering dominates. The solid line shown for low doping levels (below  $5 \times 10^{15}$

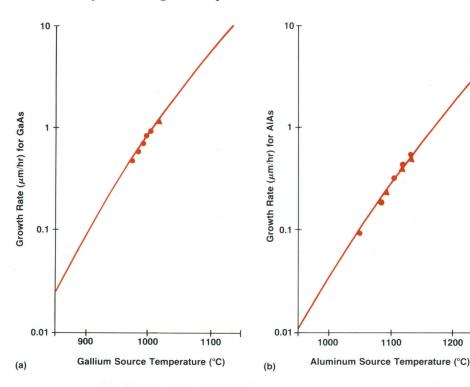

Fig. 6. Growth rate as a function of (a) gallium and (b) aluminum source temperatures. The symbols represent data for different growths and the solid lines represent the relative temperature dependencies of the vapor pressures of (a) gallium and (b) aluminum

1200

${\rm cm}^{-3}$ ) represents mobilities for extremely high-purity GaAs grown by the AsCl $_3$  vapor phase epitaxy (VPE) technique. It is clear that the MBE GaAs compares very favorably with the high-purity VPE material.

The control of the MBE growth of  ${\rm Al_xGa_{1-x}As}$  is demonstrated in Fig. 6 where growth rate is shown as a function of gallium (Fig. 6a) and aluminum (Fig. 6b) source temperatures. The symbols represent experimental data for different growths. The solid curves represent the relative temperature dependencies of the vapor pressures of gallium and aluminum. Thus, by appropriate choices for the gallium and aluminum source temperatures, both growth rate and alloy composition of GaAs and  ${\rm Al_xGa_{1-x}As}$  can be readily controlled and reproduced using MBE.

#### **Acknowledgments**

The successful development and application of a technology such as MBE can only be achieved through effective teamwork. I am very grateful to Midori Kanemura, Marge Pustorino, Dan Mars, Jeff Miller, Bob Lacoste, and Tom

Low of Hewlett-Packard Laboratories and George Patterson of HP's Microwave Technology Division for their contributions to these efforts.

#### References

- 1. P.E. Luscher and D.M. Collins, "Design Considerations for Molecular Beam Epitaxy Systems," Progress in Crystal Growth and Characterization, Vol. 2, 1979, pp. 15-32.

- 2. A.Y. Cho and J.R. Arthur, "Molecular Beam Epitaxy," Progress in Solid-State Chemistry, Vol. 10, Part 3, 1975, pp. 157-191.

- 3. S. Kofol, et al, "GaAs/AlGaAs Heterojunction Bipolar Transistors with Very Low Base Sheet Resistance," 1984 IEEE International Electron Devices Meeting Technical Digest, pp. 198-200.

- 4. S.M. Sze, Physics of Semiconductor Devices, Wiley-Interscience, New York, 1969, pp. 42-46.

- 5. D.M. Collins, "On the Use of 'Downward-Looking' Sources in MBE Systems," Journal of Vacuum Science and Technology, Vol. 20, no. 2, 1982, pp. 250-251.

- 6. G.E. Stillman and C.M. Wolfe, "Electrical Characterization of Epitaxial Layers," Thin Solid Films, Vol. 31, 1976, pp. 69-88.

# Extending Millimeter-Wave Diode Operation to 110 GHz

by Eric R. Ehlers, Sigurd W. Johnsen, and Douglas A. Gray

N THE LATE 1970s, silicon Schottky diodes and point contacts dominated diode applications in the microwave and low millimeter-wave range of frequencies. By using carefully designed microwave structures, performance well into the millimeter-wave range could be achieved. This performance, however, did not come easily. These structures were difficult to reproduce and as a result were very expensive. The small diode structures were also sensitive to damage by electrostatic discharge (ESD). Although Schottky diode pairs and quads were readily available, diodes integrated with other circuit elements could not be obtained as off-the-shelf components.

When HP launched its effort to develop a family of diodes particularly suited to millimeter-wave applications, we wanted a device that could be readily integrated into a microwave structure, was rugged and capable of handling high drive levels for multiplier applications, and had at least the sensitivity of presently available diodes.

#### **Diode Technology**

To meet the project goals of designing low-capacitance, high-power-handling diodes suitable for small-scale integrated circuits, the selection of material technology was of paramount importance. Although silicon technology was very mature and some silicon devices did exist for applications up to 40 GHz, the high parasitic capacitance of silicon

substrates made it difficult to integrate other circuit elements and beam leads without sacrificing high-frequency performance or power handling. It was clear that the design and fabrication of a useful device up to 110 GHz (W-band) required a different material technology.

The III-V compound semiconductor gallium arsenide (GaAs) offers several advantages over silicon. The intrinsic doping in GaAs is two orders of magnitude lower than

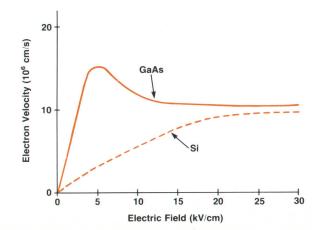

Fig. 1. Electron velocity in gallium arsenide and silicon.

Fig. 2. Cross section of sintered Schottky barrier diode.

silicon. This results in a much higher substrate resistivity and lower parasitic capacitance effects. The lower parasitic capacitance of GaAs substrates is critical. It allows the design of larger devices with increased power handling capabilities without degrading frequency performance.

Another advantage of GaAs is its higher electron mobility (see Fig. 1). This higher mobility translates up to a  $5 \times$  higher electron velocity in GaAs compared to silicon. This leads to much lower carrier transit times and makes it possible to design devices exhibiting cutoff frequencies in excess of 1000 GHz.

For these reasons GaAs was the material of choice for the millimeter-wave diode project. There was a major disadvantage, however, because a primary goal of the project was to design low-barrier and medium-barrier diodes which are commonly used in mixer and detector applications. Although HP has been very active in GaAs research and development (HP instrumentation has been shipped using internal GaAs FET and diode technology since the early 1970s), a reliable method of repeatably fabricating a modified barrier diode on GaAs presented a major technical challenge.

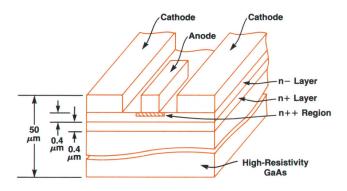

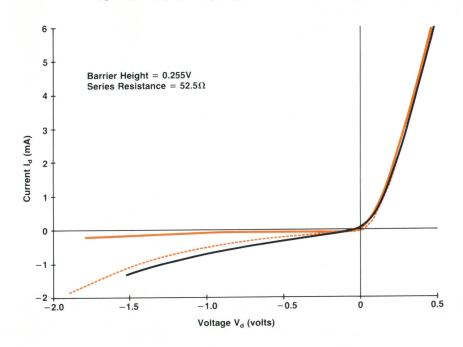

The difficulties in fabricating modified barrier diodes on GaAs were overcome by a two-phase approach. Standard Schottky barrier diodes are fabricated using liquid-phase epitaxy to grow the double n-on-n+ layers required for millimeter-wave IC fabrication. Low-barrier Schottky diodes were originally fabricated using the same epitaxial layers, but with a proprietary Schottky barrier metallization (Fig. 2). The low-barrier diode was formed by a sintering process after the Schottky metal was patterned. The sintering formed a thin, heavily doped n + layer under the anode which lowered the barrier height to the desired value (see Fig. 3). This process led to the introduction of a 26-GHz-to-40-GHz zero-biased detector fully integrated on one GaAs chip (see box on page 13). The sintering process was, however, very difficult to control and the devices were extremely sensitive to ESD, which resulted in relatively low yields during microcircuit assembly. However, even with the low yields, this device represented a significant advance in the state of the art of millimeter-wave device technology.

The second generation of modified barrier diodes was made possible by the capabilities provided by molecular beam epitaxy (MBE, see article on page 4). MBE technology provides the means for very controlled growth of the epitaxial layers required for the fabrication of planar doped barrier diodes (also called modified barrier diodes by HP). These diodes are formed by growing a multilayer GaAs epitaxial structure sandwiched between two low-resistance contacts (see Fig. 4). The design of the epitaxial structure

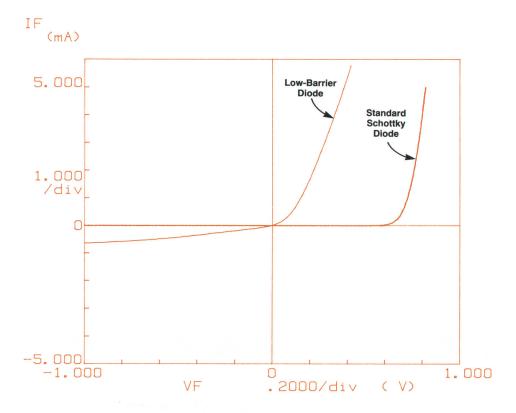

**Fig. 3.** *I-V* characteristics for standard Schottky diode and sintered low-barrier version.

**Fig. 4.** (a) Cross section of planar doped barrier diode fabricated by molecular beam epitaxy (MBE). (b) I-V characteristic.

determines the barrier height of the diode. Therefore, extremely tight control of epitaxial layer doping and thickness is required. Epitaxial layers as thin as 4 nm must be grown with abrupt transitions between layers. This critical step in the fabrication of modified barrier diodes has been moved out of the process lab and placed on the shoulders of the computer-controlled MBE system. The state of MBE

technology at HP has demonstrated its consistent performance to these demanding specifications, enabling the design and fabrication of device structures for both low-barrier and medium-barrier diode applications.

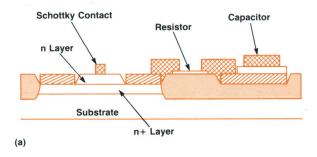

With the technology in place for manufacturing GaAs diodes with varying barrier heights, the next step was to provide the capability for fully integrated solutions of some standard millimeter-wave circuit functions. Most of the millimeter-wave circuits used in instrumentation are samplers, mixers, multipliers, and detectors. At frequencies above 26 GHz, the repeatability of hybrid assembly techniques is critical. A slight variation in a bond-wire length can be a significant fraction of a wavelength at these frequencies. The integration of a millimeter-wave diode, resistors, and capacitors on a single GaAs chip with beam leads for thin-film circuit interconnects offers superior performance in phase matching for samplers and greatly reduces the complexity and assembly costs of millimeterwave hybrid circuits. The integration process developed provides the circuit designer with the flexibility for integrating silicon nitride capacitors with values up to 20 pF and tantalum nitride resistors with a sheet resistivity of 50  $\Omega/\square$ .

The technology is directed toward allowing design engineers working on new millimeter-wave test instruments to design their own custom integrated circuits. There are some roadblocks, however. A designer must work very closely with the IC facility to make sure process guidelines or limits are not violated by the design. This can be the most time-consuming and frustrating part of the design stage. There is also a fear of the high development costs that are normally associated with a custom IC design. This factor is especially a concern at millimeter-wave frequencies where current computer-aided-design techniques are not sufficient to ensure a successful circuit design on the first try.

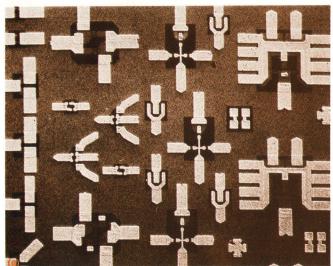

To lessen some of these difficulties and to encourage the use of this technology at HP, it was decided to offer it in a prototype mode. In this approach, circuit designers can

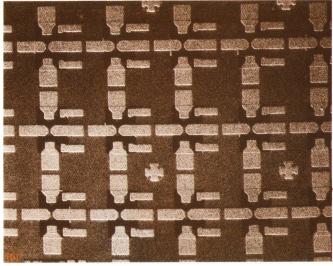

**Fig. 5.** (a) Composite mask for prototyping modified barrier diode IC designs. (b) Production mask used for volume production of successful designs.

# 26.5-to-40-GHz Waveguide Detector

In 1983 Hewlett-Packard introduced the HP 11664D 26.5-to-40-GHz waveguide detector for the HP 8756A Scalar Network Analyzer. The HP 11664D uses a Schottky diode with a barrier height modified by a sintering process in an integrated detector circuit. This circuit has proven reliable in three years of use in the field. However, manufacturing costs of the product are high because of difficulties in controlling the device fabrication process and losses in assembly caused by static electricity discharges. The new diodes, described in the accompanying article, are significantly easier to manufacture, and losses during assembly are reduced by a more rugged structure.

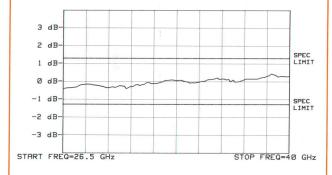

Fig. 1. Typical return loss (a) and flatness (b) of HP 11664D Detector.

#### **Experience**

To date, manufacturing losses during assembly with the sintered diodes has occasionally run as high as 50%. Under the same conditions, there have been no failures of the new modified barrier diodes. This is attributed to the tenfold reduction in electrostatic susceptibility of these diodes. Slightly lower capacitance has also led to an improvement in the frequency response of the HP 11664D. The lower capacitance allowed a small assembly change that resulted in a 1.0-dB improvement in flatness as a function of frequency. These diodes also have a more predictable voltage response as a function of input power. This allows improved dynamic accuracy for the HP 11664D. Fig. 1 shows typical return loss and flatness of the HP 11664D Detector.

#### Reference

1. C.C. Chang, et al, "A Zero-Bias GaAs Millimeter-Wave Integrated Detector Circuit," *IEEE Microwave Theory and Techniques Symposium Digest*, 1982.

Herb Upham

Development Engineer

Microwave Technology Division

design custom devices using the components supported in the integrated diode process and optimize the design for their specific application. The design is first placed on a composite mask set (Fig. 5a) with many other custom integrated diodes. This composite mask set is fabricated to supply the various designers with a small number of samples of their design for evaluation. If another design iteration is required, the redesigned device is placed on another composite mask for another cycle of prototype samples. This spreads out the development cost of the custom devices to all the designers using a composite mask. It makes it more affordable to do several design iterations or even try a high-risk design idea. Once a design is optimized and assigned to an instrument project, it is stepped onto a dedicated mask set (Fig. 5b) for higher-volume production.

The development of this integrated diode technology was very closely linked with several instrument development projects. The HP 8510A Network Analyzer and the HP 5350A/51A/52A Frequency Counters¹ rely on GaAs integrated samplers for down-conversion. The design of the HP 11970/71 Harmonic Mixers and the HP 83554A/5A/6A Millimeter-Wave Sources, which both cover the waveguide bands up to 60 GHz, also relies heavily on these Schottky barrier diode ICs. A major milestone, however, was the development of the planar doped barrier diode which enabled HP to design the HP 11970V/W Harmonic Mixers that allow spectrum measurements up to 110 GHz.

#### **Planar Doped Barrier Diode Applications**

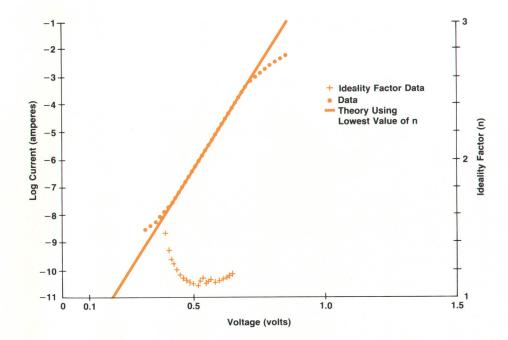

Special features of these modified barrier diodes make them ideally suited for certain key millimeter-wave products. Before discussing these applications, however, it should be pointed out that in terms of their terminal voltage and current characteristics at low frequencies, these diodes are very similar to conventional pn junction diodes and metal-semiconductor Schottky diodes. In forward bias, they closely follow the ideal diode equation as illustrated in Fig. 3:

$$I = I_o \left[ \exp \left( (V - IR_s)/nV_t \right) - 1 \right]$$

where  $I_o$  is the saturation current, n is the ideality factor (typically 1.2 for these modified barrier diodes),  $R_s$  is the series resistance, and  $V_t$  is the thermal voltage (0.026V at 300K). In reverse bias, the low-barrier versions of these modified barrier diodes deviate from this ideal equation and exhibit a "soft" breakdown characteristic caused by the variation of barrier height with bias (see Fig. 3).

The most important feature of the planar doped barrier diodes is that their barrier heights are adjustable by controlling the thickness and doping of the epitaxial layers. Changing the barrier height is equivalent to varying the saturation current and hence the turn-on voltage of the diode. Controlling the turn-on voltage is highly desirable for certain applications. One of these applications is the unbiased harmonic mixer (see article on page 22). For this application it is critical that the conduction angle (the number of degrees during each local oscillator (LO) cycle that the diode is on) be controlled precisely, and for a given LO power the conduction angle is controlled by the barrier height.

Another application that requires a low barrier height is

the broadband unbiased detector. Diode detectors are widely used at microwave and millimeter-wave frequencies as power meter sensors, scalar network analyzer detectors, and parts of leveling circuits for sources. To work well as an unbiased detector, a diode must essentially be turned on at zero volts. This implies a high saturation current and a low barrier height. A critical specification for these diodes is the video resistance  $R_{\rm v}$ , which can be defined as the incremental resistance of the diode at a bias of zero volts. For most detector applications  $R_{\rm v}$  must be between  $500\Omega$  and 5 k $\Omega$ . This requires precise control of barrier height and is an ideal application for planar doped barrier diodes.

An important parameter for microwave and millimeterwave diodes is junction capacitance, which must be kept as small as possible. Like a Schottky diode, a modified barrier diode has no minority charge storage capacitance, so the junction capacitance is quite low. The reverse-bias capacitance of a modified barrier diode is determined primarily by the dielectric constant of GaAs and the thickness of the intrinsic layer and has less variation with bias than Schottky diodes. The typical junction capacitance of a modified barrier diode with an active area of 40  $\mu\mathrm{m}^2$  is only 25 femtofarads at a bias of zero volts, and with an effective series resistance of about 20 ohms, these diodes work well in detector applications at frequencies up to 110

GH<sub>7</sub>

The modified barrier diodes are remarkably rugged devices. Physically, they have good beam-lead pull strengths of over 5 grams and a passivation that allows them to be used in nonhermetic packages. Electrically, they can reliably operate at high current densities; the diodes used in the millimeter-wave mixers described in the article on page 22 are rated to operate continuously at 16 dBm of LO power, which corresponds to average currents through the diodes of over 16 mA. These diodes are also relatively insensitive to damage caused by electrostatic discharge (ESD).

The fact that modified barrier diodes are available with integrated resistors and capacitors enhances their usefulness to the design engineer. Integrating resistors and capacitors with closely matched diodes can, in many cases, improve the performance of a product and lower its cost by decreasing parts count and shortening assembly times. The development and production of these modified barrier diode circuits provides the millimeter-wave designer with a new tool for the design of detectors and mixers up to 110 GHz.

#### Reference

1. S.R. Gibson, "Gallium Arsenide Lowers Cost and Improves Performance of Microwave Counters," *Hewlett-Packard Journal*, Vol. 37, no. 2, February 1986.

# Diode Integrated Circuits for Millimeter-Wave Applications

GaAs diode integrated circuits based on metalsemiconductor (Schottky) or modified barrier diodes have now extended the operating frequency range of small-scale ICs beyond 100 GHz. These circuits, which form the basis for many of HP's new millimeter-wave instruments, are useful for nonlinear and frequency-translation applications.

by Mark P. Zurakowski, Domingo A. Figueredo, Scott S. Elliott, George A. Patterson, William J. Anklam, and Susan R. Sloan

ALLIUM ARSENIDE (GaAs) has become the material of choice for building devices or integrated circuits for operation at frequencies higher than a few gigahertz. Several manufacturers, or foundries, are now offering design and processing services for small-scale to medium-scale integrated circuits on GaAs operating to frequencies as high as 10 GHz and HP has developed a technology for the design and fabrication of diode integrated circuits on GaAs that operate to above 100 GHz. These

circuits contain no linear gain elements such as transistors; instead they are composed of diodes, resistors, capacitors, and conductive transmission lines. Their design makes them very useful for signal detection, mixing, multiplication, sampling, power limiting, and other frequency-translating or nonlinear circuits in the millimeter-wave frequency range.

The millimeter-wave region of the electromagnetic spectrum is generally considered to span the frequency range

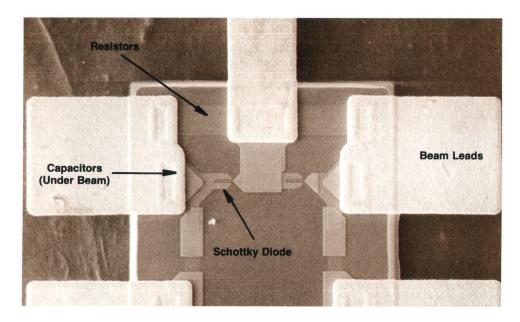

Fig. 1. Scanning electron microscope (SEM) photomicrograph of a GaAs Schottky barrier diode integrated circuit.

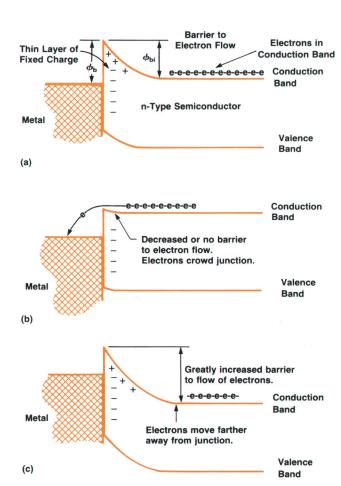

**Fig. 2.** Energy band diagrams of a metal-semiconductor (Schottky) junction for various bias conditions. (a) Zero bias. (b) Forward bias. The barrier height is decreased and electrons flow easily across the junction. (c) Reverse bias. The barrier becomes more pronounced and the electrons move farther away from the junction.

of 26 GHz to about 300 GHz, a region in which the wavelength of electromagnetic radiation is of the order of a few millimeters in free space. This region is rapidly gaining importance for uses such as high-speed digital communication, high-resolution radar, military guidance systems, and radio astronomy. Unfortunately, circuit elements such as transistors are available only for the very low end of this frequency band and even small-scale integrated circuits have been virtually unobtainable.

Millimeter-wave frequencies are so high that microwavetype hybrid circuits are difficult to construct. Even the smallest of elements or bond wires can be a significant fraction of a wavelength long and therefore can no longer be modeled as a lumped element. The resulting parasitic capacitances and inductances can completely alter the electrical performance of a hybrid circuit, rendering it unrepeatable, unreliable, and sensitive to its environment. In addition, some applications require symmetry and phasematching, which are very difficult to achieve in hybrid circuits. Hence, most designs at millimeter-wave frequencies have been done in metal or dielectric waveguide using expensive machined transitions to do the signal processing.

To date, the most important signal processing circuits for millimeter-wave applications are frequency-translating circuits—those circuits used to impress or multiplex lower-frequency information on a millimeter-wave carrier signal, or to shift the information from the millimeter-wave band down to a lower frequency where sophisticated signal processing such as amplification or filtering can be done. These translation functions can be handled very elegantly using diode integrated circuit technology.

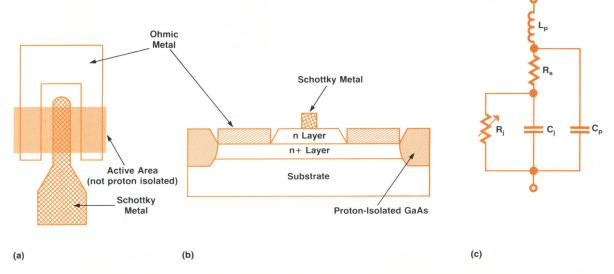

A diode integrated circuit is composed of one or more diodes in combination with resistive strips, conductive lines, and capacitive elements patterned in accordance with a set of design rules. Two layers of metallization are presently available, allowing the realization of nonplanar circuit geometries. The completed component is a small pellet of GaAs with beam leads which allow high-strength, low-parasitic bonding to a waveguide or substrate. A photo-

Fig. 3. Typical Schottky diode I-V characteristic. The straight line illustrates classic behavior. The deviation from the line for actual devices is caused by leakage current for low-current levels and by series resistance for high-current levels.

micrograph of a sample chip is shown in Fig. 1.

#### **Schottky Barrier Diodes**

All of the circuit applications mentioned above require one or more nonlinear circuit elements that operate at millimeter-wave frequencies. GaAs Schottky barrier diodes are a good choice for such high-frequency operation because of the higher velocities at which electrons travel in GaAs combined with the low charge storage effects exhibited by these diodes.

A Schottky barrier is formed whenever a metal makes contact with a semiconductor surface. Ideally, equalization of the metal and semiconductor (n type) Fermi levels causes the transfer of electrons from the semiconductor into the metal, depleting the semiconductor of mobile charge car-

riers and generating a positive space charge region. This causes the energy bands in the semiconductor (Fig. 2) to bend up at the interface, which creates a barrier potential dependent on the work function of the metal. Besides this fundamental process, if there are large numbers of surface states present on the semiconductor, then instead of electron transfer to the metal, it is electron transfer to the surface states that causes carrier depletion in the semiconductor and band bending near its surface. Fig. 2a shows the negatively charged surface states as minus signs at the metal/semiconductor interface. If the density of surface states is sufficiently large, the barrier potential becomes virtually independent of the metal's work function. GaAs falls into this category; the surface states are generated by damage caused by the metal deposition.

**Fig. 4.** Single Schottky diode. (a) Top view. (b) Cross section. (c) Equivalent circuit.  $R_j$  represents the nonlinear, exponential part of the circuit,  $R_s$  the series resistance,  $C_j$  the junction capacitance,  $C_p$  the parasitic capacitance, and  $L_p$  the beam lead inductance.

An externally applied voltage will alter the barrier potential for electrons flowing from the semiconductor into the metal. Under forward bias, the conduction band is bent upward, allowing electrons to flow freely into the metal (Fig. 2b). Under reverse bias, the Schottky barrier potential prevents electron flow from the metal to the semiconductor (Fig. 2c). The current flow is governed by thermionic emission of electrons from the semiconductor into the metal with a current-versus-voltage relationship described by:

$$J = J_o[\exp(qV/nkT) - 1]$$

(1)

where J is the current density in A/cm², J₀ is the reverse saturation current density, T is the temperature in K, q is the electron charge in coulombs, V is the applied voltage, and k is Boltzmann's constant. The ideality factor n, typically 1.1 to 1.2, accounts for tunneling currents and other nonideal behavior. J₀ is given by the expression: J₀ =  $A*T^2$  exp( $-q\phi_b/kT$ ) where  $\phi_b$  is the barrier height and A\* is Richardson's constant given by  $A* = 4\pi qm*k^2/h^3$  where m\* is the effective mass of the charge carrier (in this case an electron) and h is Planck's constant. A typical I-V characteristic is shown in Fig. 3 along with a plot of the ideality factor n as a function of bias.

A single Schottky diode and its equivalent circuit are shown in Fig. 4. The nonlinear I-V characteristic of equation 1 is modeled by a voltage dependent nonlinear resistor  $R_j$ . The junction capacitance  $C_j$  of the diode depletion region is voltage dependent and for uniformly doped epitaxial layers is given by:

$$C_i = C_{io} / \sqrt{1 - (V/\phi_{bi})}$$

and

$$C_{io} = A\sqrt{q \epsilon N_d/2\phi_{bi}}$$

where  $\phi_{bi}$  is the built-in potential (Fig. 2),  $C_{jo}$  is the zero-bias capacitance, A is the area of the junction,  $N_d$  is the doping of the epitaxial layer, and  $\epsilon$  is the dielectric constant of the semiconductor. The parasitic elements are the series resistance  $R_s$  and the beam-lead/Schottky-ohmic inductance  $L_p$  and capacitance  $C_p$ . Major contributors to  $R_s$  are contact resistances, the undepleted epitaxial layer resistance, and metal layer resistances. Minimizing the effects of the par-

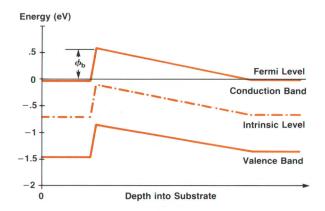

Fig. 5. Energy band diagram of a modified barrier diode at zero bias.

asitic elements is extremely important since, with  $C_j$ , they set an upper limit to the frequency of operation.

#### **Modified Barrier Diodes**

In many product applications, high-speed, variable-barrier-height diodes are very desirable because of the added flexibility they provide in choosing optimum response, bias conditions, and power-handling capability. In the case of standard GaAs Schottky diodes, this flexibility is almost nonexistent because the barrier height is virtually independent of the metal system used for the Schottky contact. To address the variable-barrier needs of HP's millimeter-wave customers, a new device called a modified barrier diode has been developed that allows a designer to choose diode barrier heights between 0.2 eV and 1.2 eV. Production of modified barrier diodes requires a technique called molecular beam epitaxy (MBE, see article on page 4) to grow extremely thin, highly doped layers. The major advantage provided by MBE is that the number of fixed charges introduced into the layer determining the barrier height is very accurately controlled by this layer's doping and thickness.

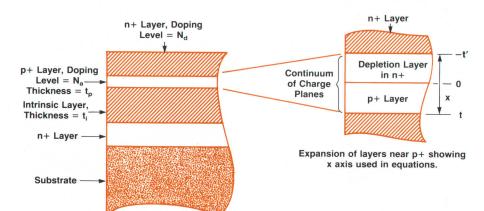

The energy band diagram for a modified barrier diode is triangular in shape as depicted in Fig. 5. It is very similar to the diagram for a Schottky diode and, with good approximation, Equation 1 can also be used for modified barrier diodes. All that is needed is an equation relating doping levels and layer thickness to barrier height. The epitaxial

**Fig. 6.** Cross section of modified barrier diode fabricated using molecular beam epitaxy (MBE).

layers forming the modified barrier diode and the variables that will be used in the following simple theory of operation are shown in Fig. 6. Gauss' Law is applied using the following assumptions:

- Depletion approximation. That is, all space-charge regions are fully depleted (no mobile charge carriers) and have abrupt boundaries.

- Infinite planes of charge.

- All dopings are uniform for simplicity of integration.

- Charges are not discrete but spread throughout the layers.

- The bottom layer is far from the barrier and does not enter into the calculation.

The last assumption allows the I-V equation for the modified barrier to have the same form as for the Schottky barrier.

Gauss' Law:

$$\oint \mathbf{E} \cdot \mathbf{n} ds = \frac{1}{\epsilon} \sum_{i=1}^{\infty} q$$

yields  $E=\sigma/2$  for an infinite plane of charge where E is the electric field, n is the normal to the plane,  $\sigma$  is the sheet charge density, and  $\varepsilon$  represents the semiconductor dielectric constant.

For the structure shown in Fig. 6, there is a continuum of charge planes. Thus:

$$E = (2qN_at - 2qN_ax)(1/2\epsilon)$$

for  $0 \le x \le t$

$$E = (2qN_at + 2qN_dx)(1/2\epsilon)$$

for  $-t' \le x \le 0$

where  $N_a$  is the volume density of acceptor ions,  $N_d$  is the volume density of donor ions, t is the thickness of the p+ layer, and t' is the thickness of the n+ layer.

Integrating E from -t' to t and using  $t' = t(N_a/N_d)$  from charge balance, we obtain:

$$-\phi_{\rm b} = (1/2\epsilon) \left[ N_{\rm a} + (N_{\rm a}^2/N_{\rm d}) \right] t^2 \tag{2}$$

**Fig. 8.** Cross section of modified barrier diode. Equivalent circuit and element definitions same as for Fig. 4.

This equation gives the approximate barrier height of a modified barrier diode and can be substituted directly into Equation 1 for the Schottky diode I-V characteristic.

Comparison of a measured I-V characteristic with a curve predicted by the simple theory presented above is shown in Fig. 7. The reverse characteristics are not modeled well by the simple theory for low-barrier diodes because the simple theory neglects the effect of the electrons in the intrinsic region on the barrier height. In reality the barrier height is lowered slightly in the reverse bias direction and raised slightly in the forward bias direction. This can be taken into account using Stanford University's SEDAN (SEmiconductor Device ANalysis) modeling program. SEDAN is a one-dimensional numerical simulator which solves simultaneously the continuity equations and Poisson's equation for the electrostatic potential and carrier concentrations as a function of space and time. The third I-V characteristic in Fig. 7 is predicted by SEDAN. Notice that it predicts much higher leakage current in the reverse direction and more closely follows the actual I-V characteristic of the measured diode. The I-V characteristics for the simple theory, SEDAN, and the measured diodes all agree for the higher barrier heights since the effect of the

Fig. 7. I-V characteristic for modified barrier diode. Solid color curve is that predicted by the simple theory discussed in the text, dashed color curve is that predicted by Stanford University's SEDAN modeling program, and the solid black curve is measured data.

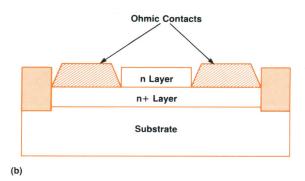

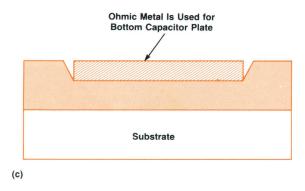

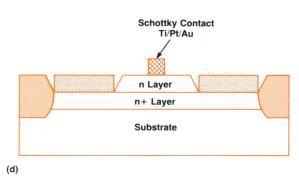

**Fig. 9.** Schottky barrier diode fabrication. (a) Nonconductive areas formed by proton isolation (hydrogen ion implantation). (b) Ohmic contacts formed by etching top layer, depositing metal in holes, and alloying metal to bottom layer. (c) The steps for (b) are used at the same time to form the bottom plates of the capacitors in the proton-isolated regions. (d) The Schottky contact is formed using a trimetal process of titanium, platinum, and gold.

barrier lowering is a much smaller portion of the intrinsic barrier height.

Fig. 8 shows a cross section of a modified barrier diode. Its corresponding circuit model is the same as that shown in Fig. 4 for a standard Schottky barrier diode, but in this case  $C_j$  is no longer dependent on the applied voltage, except for the lowest barrier diodes. For a modified barrier diode,  $C_j$  depends only on the area and intrinsic layer thickness.

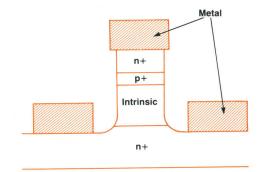

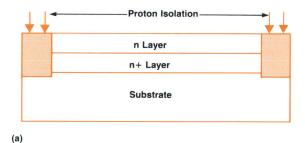

#### **Diode IC Fabrication**

Diode integrated circuits are fabricated using standard photolithographic techniques. The substrates are semi-insulating gallium arsenide wafers with reasonably low defect density. In the case of Schottky diode ICs, liquid-phase epitaxy (LPE) is used to grow single-crystal layers of doped GaAs. The first layer consists of about 300 nm of heavily doped n-type GaAs (about 10<sup>18</sup>/cm³) to serve as a bottom conducting surface for the diodes. The top layer is designed to minimize the zero bias junction capacitance while maintaining reasonably low series resistance. We typically choose this layer to be about 300 nm of 10<sup>17</sup>/cm³ n-type material.

The first step in the process is to select and isolate regions of the substrate to be used for diodes. The technique of proton isolation, or ion implantation with hydrogen ions, is used to destroy the conductivity of the epitaxial layers in all areas of the wafer except where diodes are to be located (see Fig. 9a). Holes are then etched through the top layer to the heavily doped n+ layer and metal is deposited in these holes. The metal is alloyed through a sintering step to form a low-resistance (ohmic) contact to the bottom

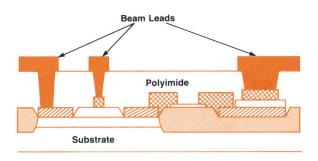

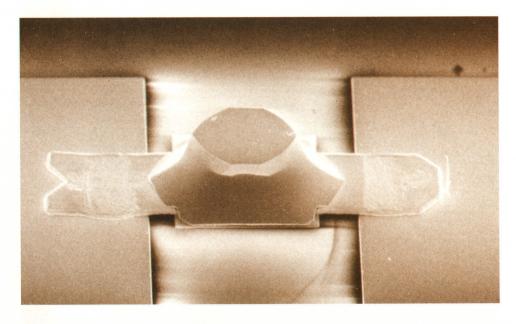

**Fig. 10.** (a) Cross section of integrated structure. (b) Structure of (a) with polyimide insulating layer and beam leads.

(b)

**Fig. 11.** Photomicrograph of completed diode IC chip mounted upside down on a microwave carrier.

layer, and thus to the bottom of the diodes (Fig. 9b).

The same etch and deposition steps used to form the ohmic contacts are also used to form the bottom plates for capacitors as shown in Fig. 9c. The GaAs etch is done in a proton isolated region of the substrate, so that the metal does not form an ohmic contact in this case. Resistive strips of tantalum nitride are formed next on the semi-insulating region of the GaAs by field deposition and selective etching. The resistivity of these films is nominally  $50\Omega/\square$ . The capacitor dielectric, consisting of about 100 nm of silicon nitride, is patterned on top of the metal bottom plate to yield a nominal capacitance density of  $0.67~\mathrm{fF}/\mu\mathrm{m}^2$ .

The critical Schottky barrier contact is now formed. A trimetal system of titanium-platinum-gold is used to form a stable and highly reliable contact that exhibits low parasitic resistance and a low potential for electromigration. The titanium adheres well to GaAs and does not easily form alloys with it. The gold is highly conductive and

extremely resistant to corrosion or electromigration, but it does interdiffuse easily with both titanium and GaAs. Therefore, a thin layer of platinum is used to separate the titanium from the gold and adheres very well to both.

Photoresist is first applied to the whole wafer and windows are defined where the metals will eventually be located. The three metals are applied sequentially in the same evaporation system, and the unwanted regions of metal are lifted off by dissolving the photoresist underneath. This process allows very good control of metal strip geometries down to around 800 nm, which is near the lower limit for optical lithography. A cross section of the resulting Schottky contact finger is shown in Fig. 9d. The same metal deposition and lift-off procedure is used to form the top plates of the capacitors and to make connections between all of the various circuit elements (see Fig. 10a).

The entire circuit is passivated and planarized by a 1- $\mu$ m

**Fig. 12.** Photomicrograph of single beam-lead diode mounted on a coplanar waveguide structure for nonlinear and linear testing at microwave frequencies.

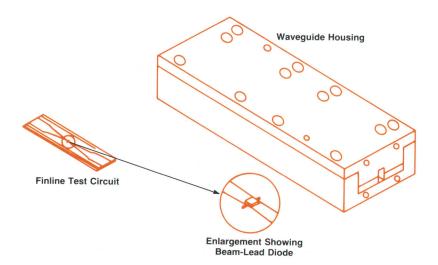

**Fig. 13.** Diagram of finline test package used to test beam-lead diodes at millimeter-wave frequencies.

thick coating of polyimide which is spun on and cured. Contacts to the outside world are made by selectively etching vias (holes) through the polyimide to the desired metal areas. Added areas of metal are photolithographically formed on top of the polyimide and plated to several micrometers thick with gold to form beam leads or a second contact metal layer (see Fig. 10b).

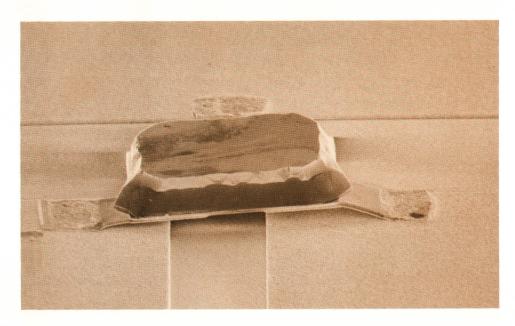

The wafer is mounted circuit-side down on a quartz wafer and backlapped carefully to a thickness of 50  $\mu$ m. A backside alignment to the patterned front surface is performed using an infrared aligner to expose photoresist which defines etch channels. A chemical etchant is then used to separate the chips and expose the gold beams. A completed chip, mounted upside down on a microwave carrier, is shown in Fig. 11.

Fabrication of modified barrier diode integrated circuits is quite similar except for the addition of a mesa etch to define the diodes and replacement of the Schottky metal deposition with a low-resistance top metal deposition and alloy.

#### **GaAs Diode IC Characterization**

During fabrication the wafers are monitored by periodically checking standard test patterns included on each mask set. The patterns are probed and dc-to-1-MHz tests are done as the IC is fabricated. From these tests we can evaluate the quality of the circuit elements at various steps in the process. Upon completion of the fabrication process, each diode IC is tested with an automated test system which screens the ICs for specified dc parameters.

Some applications require testing of parameters at microwave and millimeter-wave frequencies. This testing is more difficult and is usually done on a sample basis. A fixture useful for both linear and nonlinear testing at microwave frequencies is shown in Fig. 12 in which a single beam-lead

diode is mounted on a coplanar waveguide structure. A network analyzer can be used to measure the four s-parameters of this configuration. This data can be compared to that predicted by a linear model of the device to find the element values in the model that most closely fit. Nonlinear parameters such as harmonic generation efficiency or series power limiting can also be measured.

A fixture that has proven useful for millimeter-wave frequencies is shown in Fig. 13. This circuit consists of a finline substrate in a waveguide housing. The finline is composed of a thin film of gold on a fused silica or sapphire substrate that tapers to a narrow gap at the center. It provides a broadband, low-VSWR transition from the waveguide mode to a finline mode. A diode or diode integrated circuit can be mounted at the neck of this circuit as shown. Again, full two-port s-parameter measurements can be made over the waveguide band using a network analyzer, or nonlinear measurements can be performed.

#### Conclusion

Hewlett-Packard has developed technologies for fabrication and design of custom diode integrated circuits that operate beyond 100 GHz. These ICs form the basis for many of HP's new millimeter-wave instruments, but are not available as separate products.

#### **Acknowledgments**

Many of the original concepts of GaAs ICs using Schottky barrier diodes were developed by C.C. Chang, Gary Roberts, and Dennis Lynch. The process development work was partially due to the efforts of Nina Maddox, Mimi Planting, and Mary Stone. Much of the characterization work was done by Eric Ehlers, Tim Bagwell, and Virginia Cox. The transition to production was made possible by Mark Buswell, Janice Pryst, Sig Johnsen, and Selena Vella.

# **Unbiased Subharmonic Mixers for Millimeter-Wave Spectrum Analyzers**

by Robert J. Matreci

XTERNAL WAVEGUIDE MIXERS are used to extend the frequency range of a microwave spectrum analyzer beyond its frequency limit for a coaxial connector input. Since a microwave analyzer's local oscillator (LO) has a typical range of 2 to 6.2 GHz, the mixers must operate on higher-order harmonics of the LO. To maintain the analyzer's amplitude measurement accuracy, individual calibration and flat frequency response of the mixer are mandatory. If there are no electrical or mechanical adjustments to be made as a function of frequency (e.g., bias current or backshort position), then wideband and automated spectral measurements are possible. High burnout level and ruggedness are required for reliability.

#### **Even-Harmonic Mixer Design**

The HP 11970 family of waveguide mixers<sup>1</sup> is designed for use with the HP 8566B Spectrum Analyzer or the HP 70000 Modular Measurement System (Fig. 1). Six waveguide bands from 18 to 110 GHz are covered.

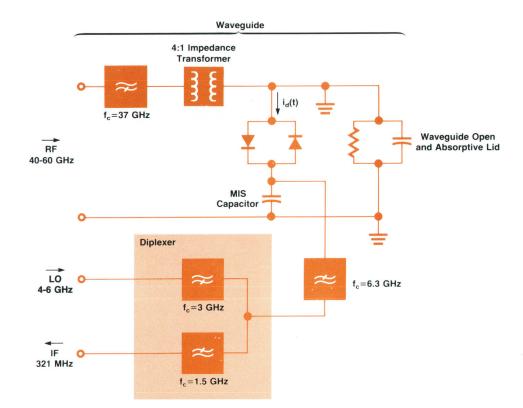

In the schematic of Fig. 2, a microstrip diplexer separates the analyzer's LO from the intermediate frequency (IF) mixing product. The RF signal enters via a tapered waveguide section which is terminated by the diodes. The antiparallel-pair diode configuration<sup>2</sup> gives improved conversion loss

over single-diode circuits since the conductance waveform symmetry produces mixing products caused only by even harmonics of the LO. Thus, less energy is lost to unused harmonics. The back-to-back diode connection also increases electrostatic voltage damage resistance.

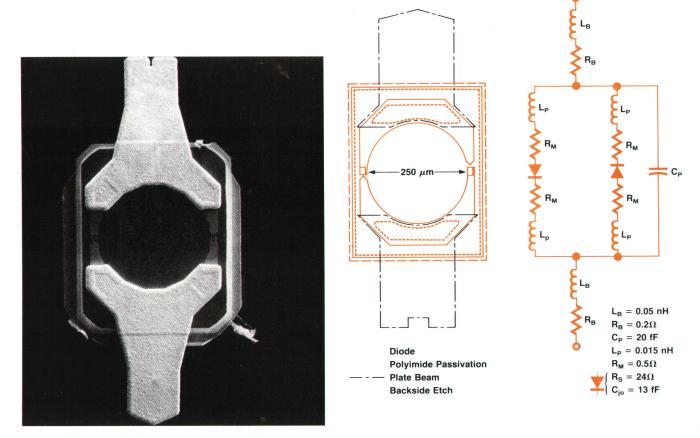

The diodes, Fig. 3, are a monolithic GaAs pair produced by HP's Microwave Technology Division. A 250- $\mu$ m-diameter loop connects the two diodes and contains the even-order current harmonics. The zero-bias capacitance  $C_{jo}$  is 13 fF per diode and the series resistance is 24 $\Omega$ . A polyimide layer passivates the diodes and contributes to the excellent beam-lead pull strength of 15 grams.

A key factor in realizing constant conversion loss versus frequency is the control of the odd harmonics of the LO produced in the diodes. Although the conductance (mixing) waveform contains only even harmonics of the LO, the input current contains only odd harmonics. If these odd harmonics propagate away from the diode's location and then reflect back from any internal or external element, the desired even harmonic can be severely weakened by the reentering signals. In previous harmonic mixers, these destructive interference effects led to numerous spike-like increases of conversion loss versus frequency, and a change in bias current or backshort position was required to move

**Fig. 1.** Four HP 11970 waveguide harmonic mixers connected to the HP 70000 Modular Measurement System.

**Fig. 2.** Schematic of U-band (40-to-60-GHz) tenth-harmonic mixer.

**Fig. 3.** Beam-lead GaAs diode. (left) Photomicrograph of diode. (center) Layout of diode. (right) Schematic representation of diode.

the reconstruction phase away from cancellation.

For the HP 11970 Mixers, odd-harmonic reflection from the diplexer and the LO source system are eliminated by the short produced at the diodes by the lumped first element of the 6.3-GHz low-pass filter (LPF, see Fig. 2). This metal-insulator-semiconductor (MIS) capacitor is also in series with the RF signal, so it must maintain its shorted condition throughout the RF band so that the entire RF voltage can appear across the diode. The capacitor's pad dimensions are 75  $\mu$ m by 75  $\mu$ m and its silicon-dioxide (SiO<sub>2</sub>) dielectric layer thickness is 440 nm. These small sizes push the capacitor's self-resonance frequency to more than 110 GHz.

The waveguide 37-GHz high-pass filter (Fig. 4) follows a symmetrical  $\exp(\cos^3\theta)$  taper,<sup>4</sup> and prevents odd LO harmonics from reflecting from the out-of-band source mismatch of the system being measured. Early in the development project, a rectangular-to-double-ridge taper was tried, but the large variation in cutoff frequency along the taper was itself a source of odd-harmonic reflection. Other especially troublesome sources are components such as bends, twists, and even the terminated arms of directional couplers, all of which present significant reflections at or below their cutoff frequency.

The high-pass filter's width taper is integrated into a

**Fig. 5.** Conversion loss versus conduction angle and LO power for the eighth and tenth harmonics of a high-barrier diode.

**Fig. 4.** A special taper (left) in the waveguide (right) acts as a 37-GHz high-pass filter and 4:1 impedance transformer. The taper is formed by numerically controlled milling machines according to equations describing the taper's dimensions.

**Fig. 6.** Conversion loss versus frequency for the 18-to-60-GHz range.

#### 11970W CALIBRATION

|   | FREQ. | CONV. LOSS | REF. LVL OFS. | FREG.  | CONV. LOSS | REF. LVL OFS. |

|---|-------|------------|---------------|--------|------------|---------------|

|   | 75.00 | 41.1       | 11.1          | 93.00  | 41.7       | 11.7          |

|   | 76.00 | 41.0       | 11.0          | 94.00  | 41.9       | 11.9          |

|   | 77.00 | 41.4       | 11.4          | 95.00  | 42.2       | 12.2          |

| ı | 78.00 | 41.2       | 11.2          | 96.00  | 42.3       | 12.3          |

|   | 79.00 | 41.4       | 11.4          | 97.00  | 42.6       | 12.6          |

|   | 80.00 | 41.4       | 11.4          | 98.00  | 42.8       | 12.8          |

| ı | 81.00 | 41.9       | 11.9          | 99.00  | 42.7       | 12.7          |

|   | 82.00 | 41.4       | 11.4          | 100.00 | 42.8       | 12.8          |

| ı | 83.00 | 41.5       | 11.5          | 101.00 | 43.0       | 13.0          |

|   | 84.00 | 41.4       | 11.4          | 102.00 | 43.1       | 13.1          |

|   | 85.00 | 41.4       | 11.4          | 103.00 | 43.4       | 13.4          |

|   | 86.00 | 41.6       | 11.6          | 104.00 | 43.6       | 13.6          |

| ı | 87.00 | 41.7       | 11.7          | 105.00 | 43.7       | 13.7          |

| ı | 88.00 | 41.5       | 11.5          | 106.00 | 43.9       | 13.9          |

|   | 89.00 | 41.5       | 11.5          | 107.00 | 44.0       | 14.0          |

|   | 90.00 | 41.2       | 11.2          | 108.00 | 44.3       | 14.3          |

|   | 91.00 | 41.5       | 11.5          | 109.00 | 44.8       | 14.6          |

|   | 92.00 | 41.6       | 11.6          | 110.00 | 43.9       | 13.9          |

**Fig. 7.** Each HP 11970 Mixer is individually calibrated for conversion loss across its full frequency band. Data is entered into the mainframe spectrum analyzer to provide corrected amplitude measurements in the millimeter-wave bands.

modified exponential waveguide height taper,<sup>5</sup> which in a minimum length lowers the waveguide impedance by a factor of 4 to match the time-average impedance of the diode.

The diodes are thermosonically bonded across the reduced waveguide opening height (0.5 mm), one terminal to the bottom wall and the other onto the MIS capacitor attached with epoxy adhesive to the top wall.

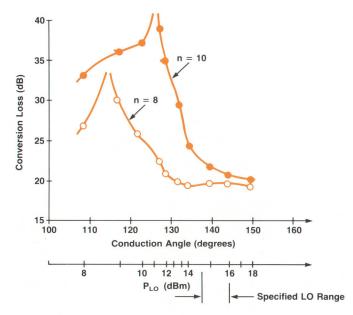

The relatively large local oscillator drive level required (14.5 dBm to 16 dBm) is a result of the high diode barrier height ( $V_f$  at 1 mA = 0.73V) and the need for a large conduction angle. Fig. 5 shows that only conduction angles greater than 140 degrees will avoid nulls in the eighth or tenth harmonic of the conduction waveform.

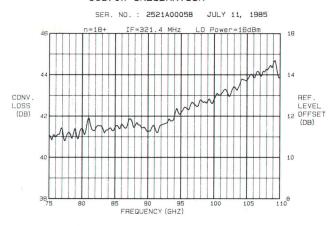

The eighteenth harmonic is required to reach the 75-to-

110-GHz band, but the conduction angle null occurs close to the standard 14.5-dBm-to-16-dBm LO power range. The conduction angle can be altered by using more LO power or reducing the barrier height of the diodes. Since the various harmonic mixers are required to be compatible with the LO drive available in the spectrum analyzer system, the medium-barrier diode ( $V_f$  at 1 mA = 0.28V) described in the articles on pages 10 and 14 was developed. This diode provides the same type of flat response and insensitivity to LO variation at 110 GHz (n = 18) as the high-barrier diode does at 18 GHz (n = 6).

#### **Performance Measurements**

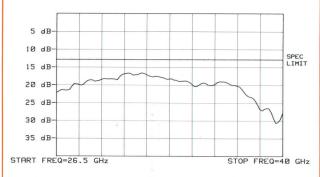

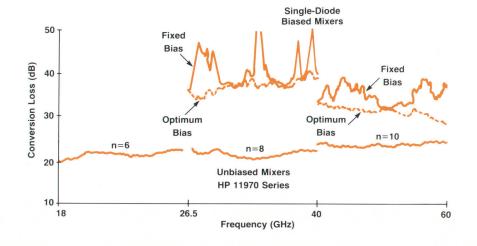

Conversion losses for each waveguide band from 18 to

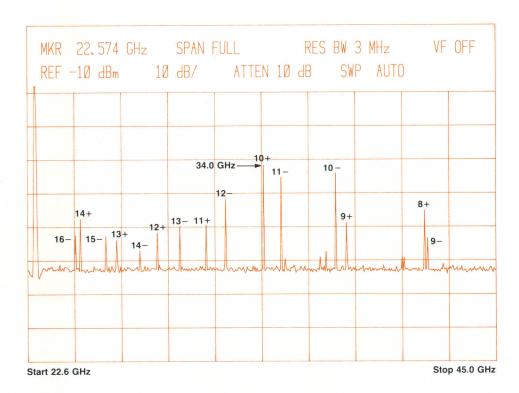

Fig. 8. A-band spectrum analyzer display of a single input frequency at 34 GHz for mixer with 321-MHz LO. Close grouping of image responses (N – harmonics) and odd-order suppresion are shown.

**Fig. 9.** A-band spectrum analyzer display for older 2.05-GHz IF harmonic mixers. Note that the image responses (N – harmonics) interleave with desired N+ harmonic responses.

60 GHz are shown in Fig. 6. To demonstrate the improved flatness and sensitivity of the unbiased HP 11970 Mixers, the plot for a single-diode biased mixer is shown for the cases of bias optimized at each frequency and a fixed bias optimized at only the center of the band. An example of the calibration chart that accompanies each HP 11970 Mixer is shown in Fig. 7 for the 75-to-110-GHz band.

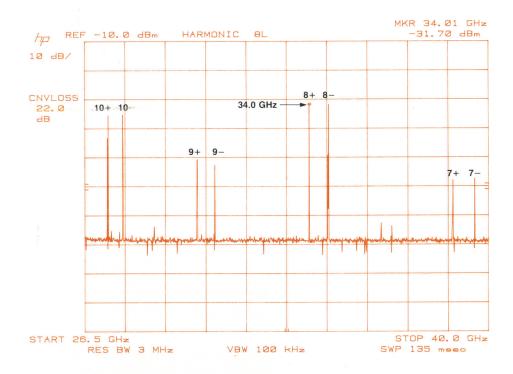

The suppression of odd-harmonic mixing products and the choice of a relatively low IF frequency (321 MHz versus 2.05 GHz used previously) aids in reducing the spectrum analyzer's display clutter. Because no RF preselectors are available for these bands, responses from harmonics adjacent to the one desired also appear. The antiparallel-pair configuration suppresses the adjacent odd responses and the low IF frequency causes the wanted N+ harmonic response and its N- harmonic image response to be grouped closely with no interleaving. The resulting full band display caused by a single input frequency has a certain "order" to it (see Fig. 8). Fig. 9 shows the same display for the earlier 2.05-GHz-IF mixers.

#### **Acknowledgments**

Kudos to C.C. Chang, Gary Roberts and Dennis Lynch for the original high-barrier diode. The medium-barrier diode group, whose articles appear in this issue, did an excellent and fast job. Vonnie Anderson aided with computer modeling. Jimmie Yarnell designed the mechanical package and processes (besides creating valuable artists' renditions). Helen Ericson and Dorothy Yanez handcrafted the prototypes. Vinh-Khuong Nguyen, Ken Lew, and Robert Charlton molded the efforts into a producible product with automated testing. Project managers Frank David and Roger Stancliff reviewed the design and Roger Kahn and Ron Rausch marketed the devices.

#### References

- 1. R. Matreci and F. David, "Unbiased, Subharmonic Mixers for MMW Spectrum Analyzers," 1983 IEEE MTTS Symposium Digest, pp. 130-132.

- 2. M. Cohn, J. Degenford, and B. Newman, "Harmonic Mixing with an Antiparallel Diode Pair," *IEEE Transactions on Microwave Theory and Techniques*, Vol. MTT-23, August 1975, pp. 667-673.

- 3. G. Anderson, et al, "GaAs Beam Lead Antiparallel Diodes for MMW Subharmonic Mixers," IEEE International Electron Devices Meeting, Washington D.C., December 1981.

- 4. C. Tang, "Nonuniform Waveguide High-pass Filters with Extremely Steep Cutoff," *IEEE Transactions on Microwave Theory and Techniques*, Vol. MTT-12, May 1964, pp. 300-309.

- 5. F. David, "Analysis and Synthesis of Exponentially Tapered, Nonuniform Transmission Line Impedance Transformers," MSEE Thesis, Oregon State University, 1975.

## **Authors**

November 1986

York, Sig now lives in Santa Rosa, California. He and his wife have two sons. His interests outside work include skiing, hiking, backpacking, and gardening.

at Madison. Her BS degree in physics and English was awarded in 1981. She continued her studies at the University of Colorado, completing work for an MS degree in physics in 1984. Susan lives in Petaluma, California and enjoys skiing, bicycling, hiking, reading, and knitting. She's also a Beatles music fan.

#### Eric R. Ehlers

Eric Ehlers came to HP in 1979 and has been an applications engineer for GaAs FETs and diode integrated circuits. He's currently an R&D engineer working on millimeter-wave products. Born in San Diego, California, he studied biology at the